User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_05.fm.(1.2)

March 27, 2006

Memory Management

Page 191 of 377

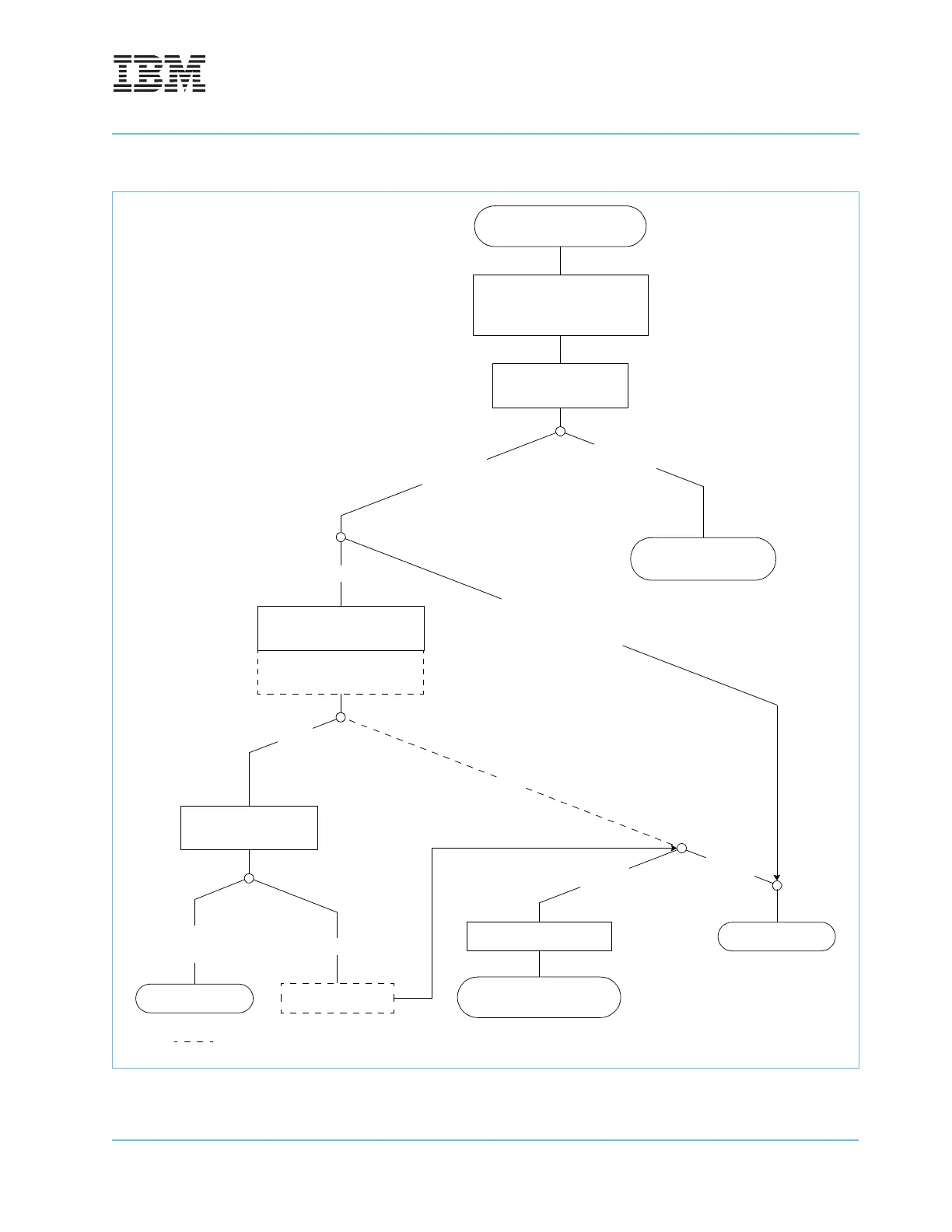

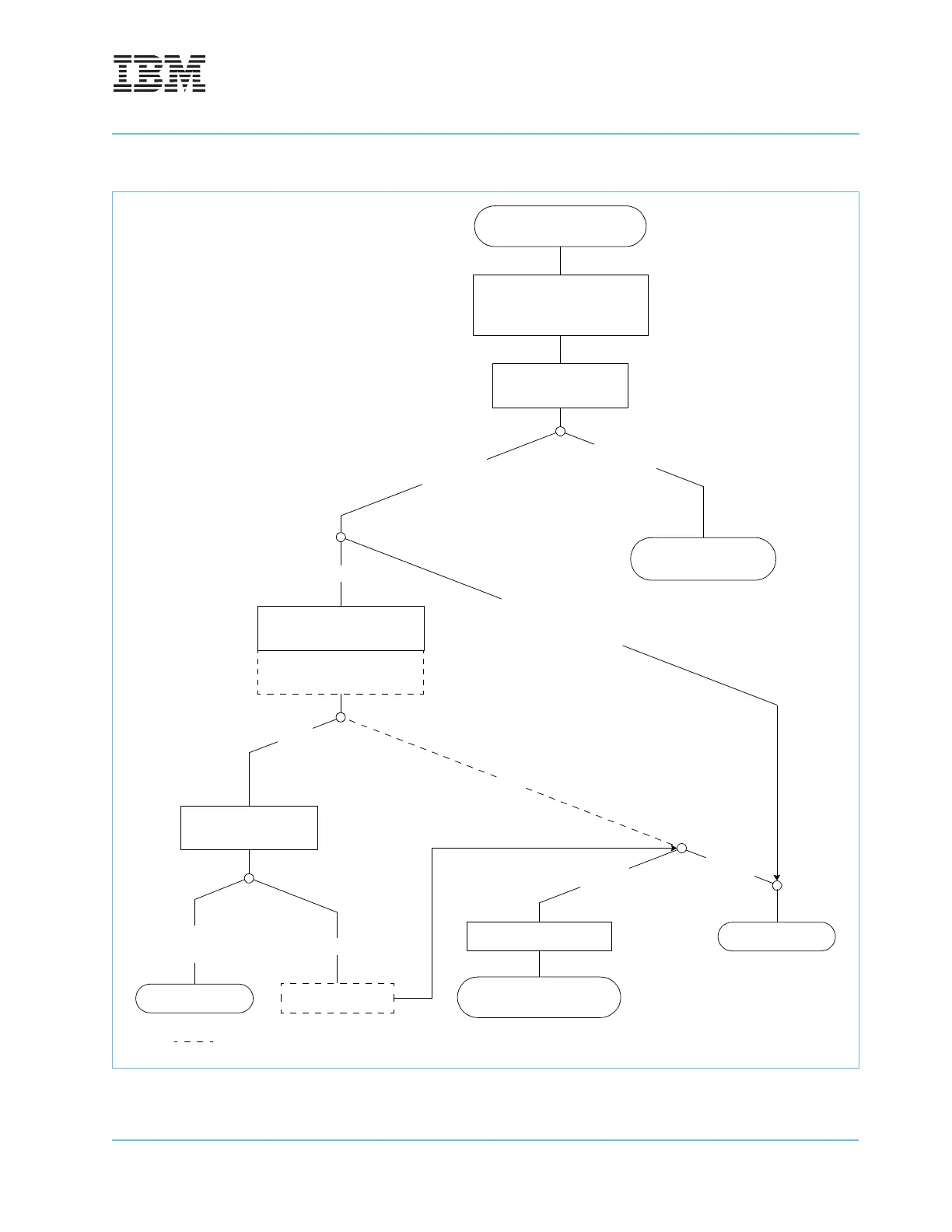

Figure 5-6. General Flow of Page and Direct-Store Interface Address Translation

Address Translation with

Segment Descriptor

Access Faulted

Access Faulted

Perform Page Table

Search Operation

Continue Access to

Memory Subsystem

Translate Address

*In the case of

instruction accesses,

causes ISI exception

Load TLB Entry

(See Figure 5-8 on page 203)

(See Figure 5-9 on page 205)

Otherwise

Check T-Bit in

Segment Descriptor

Use EA[0–3] to

Select One of 16 On-Chip

Segment Registers

Page Address

Translation

(T = 0)

Direct-Store

Segment Address

(T = 1)*

I-Fetch with N-Bit Set in

Segment Descriptor

(No-Execute)

PTE Not

Found

PTE Found

Access

Protected

Access

Permitted

Optional in the PowerPC Architecture. Implemented in the 750GX.

DSI/ISI Exception

Compare Virtual Address

with TLB Entries

Generate 52-Bit Virtual

Address from Segment

Descriptor

TLB

Hit

TLB

Miss

Loading...

Loading...