User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_06.fm.(1.2)

March 27, 2006

Instruction Timing

Page 247 of 377

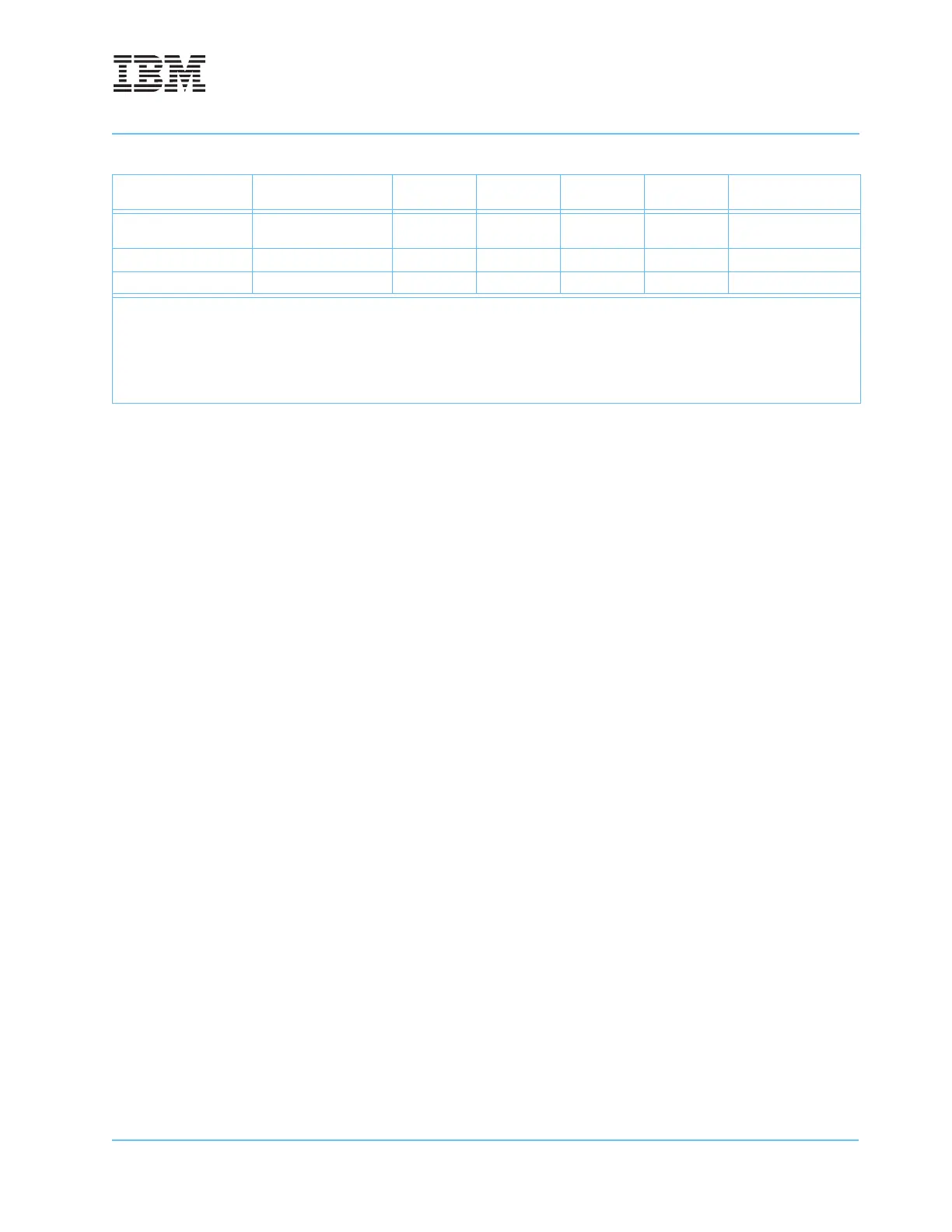

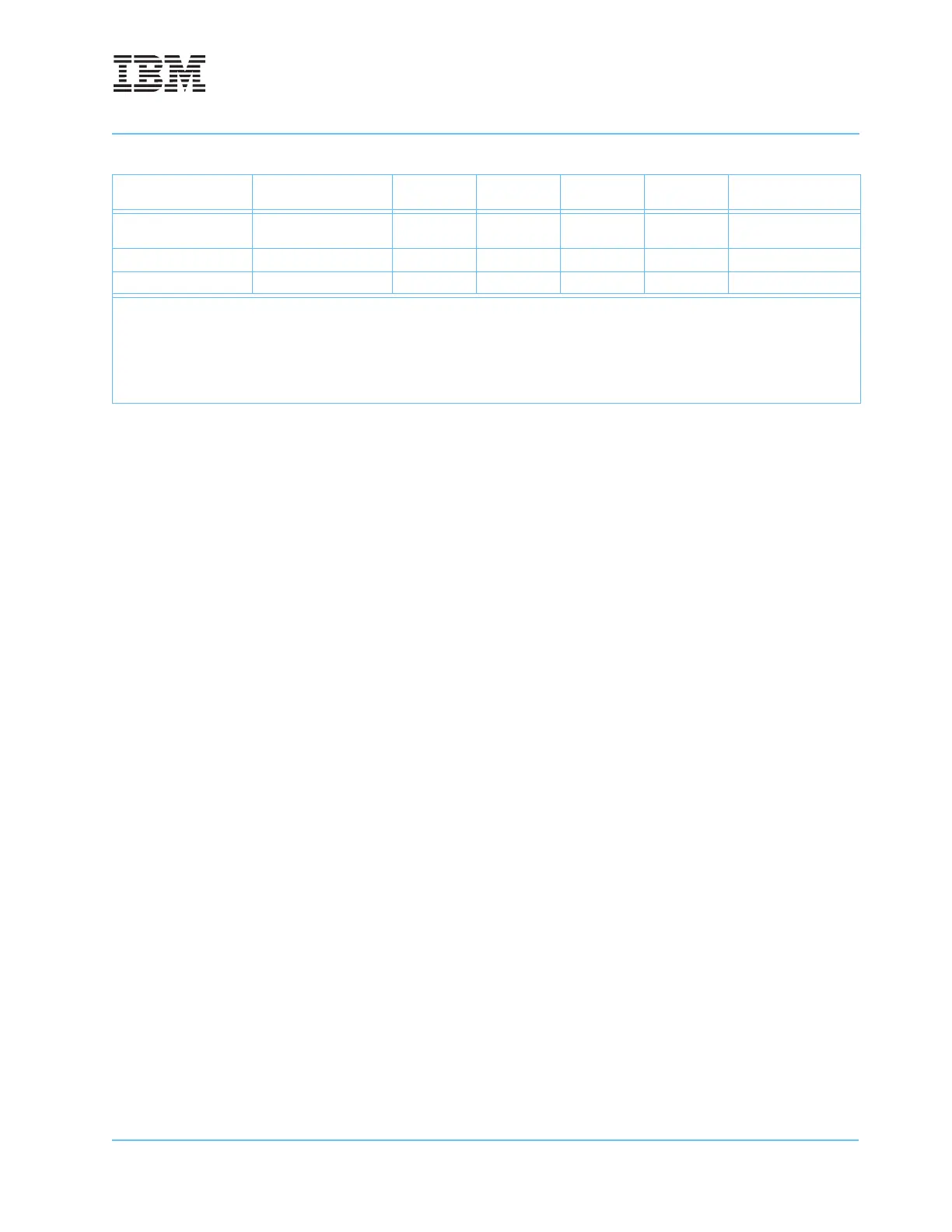

Store Word with Update

Indexed

stwux 31 183 LSU 2:1 —

Store Word Indexed stwx 31 151 LSU 2:1 —

TLB Invalidate Entry tlbie 31 306 LSU 3:4

1

Execution

Table 6-9. Load-and-Store Instructions (Page 4 of 4)

Instruction Mnemonic

Primary

Opcode

Extended

Opcode

Unit Cycles Serialization

1. For cache operations, the first number indicates the latency in finishing a single instruction; the second indicates the throughput for

back-to-back cache operations. Throughput might be larger than the initial latency, as more cycles might be needed to complete

the instruction to the cache, which stays busy keeping subsequent cache operations from executing.

2. The throughput number of six cycles for dcbz assumes it is to nonglobal (M = 0) address space. For global address space,

throughput is at least 11 cycles.

3. Load/store multiple/string instruction cycles are represented as a fixed number of cycles plus a variable number of cycles, where n

is the number of words accessed by the instruction.

Loading...

Loading...