1000BASE-T/100BASE-TX/10BASE-T Physical Layer Compliance Tests Manual

Intel Confidential 149

100Base-TX Test Procedure for the 82544 Chip

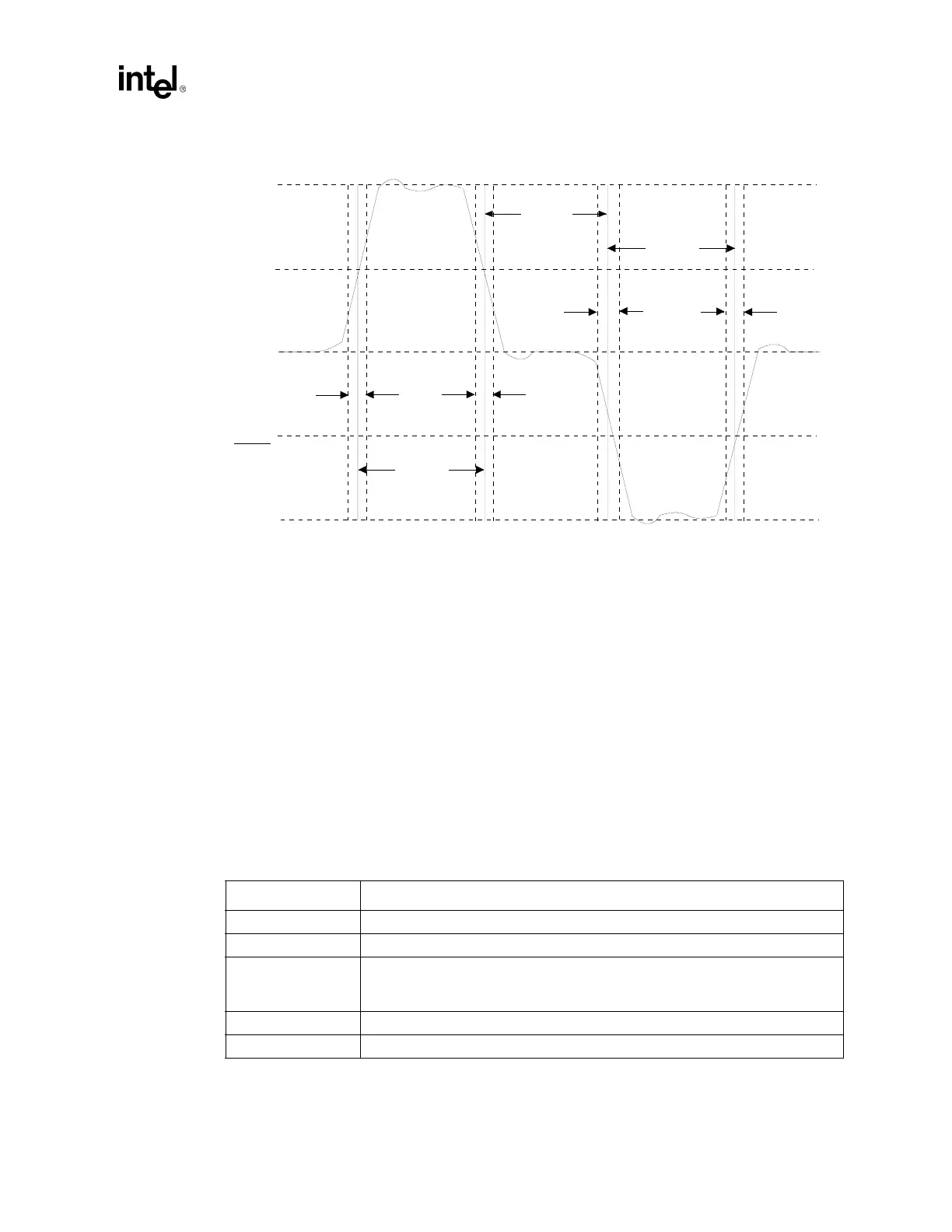

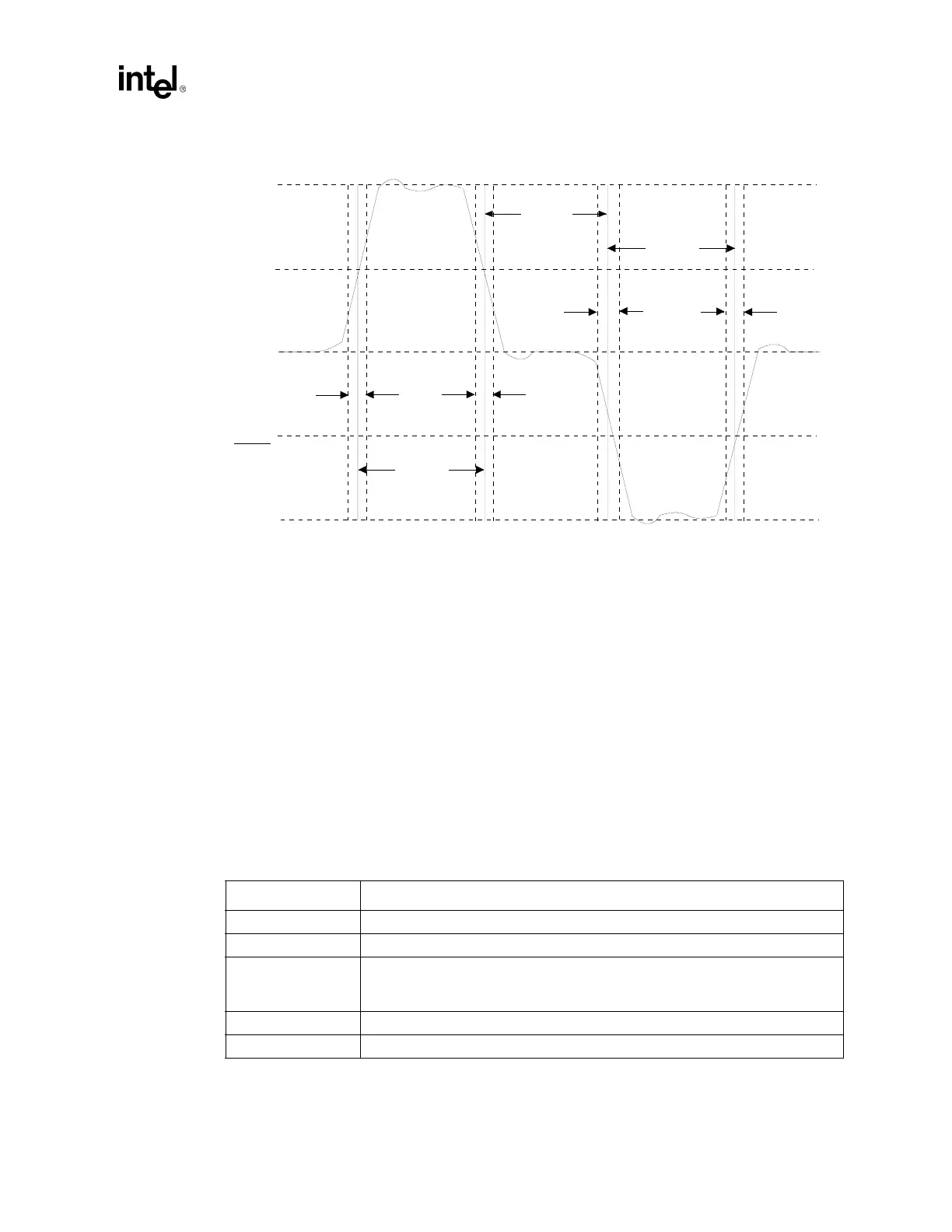

Figure I-13. Active Output Interface Duty Cycle Distortion (Figure 9-3)

I.5.6 Test Procedure

Connect the test equipment and Unit Under Test (UUT), as shown in Figure I-2. If available, use

register settings or test pins to:

•

Disable Scrambling.

•

Force 100 Mbps Good Link.

•

Transmit a hexadecimal 3,4,3,4,3,4… data pattern (creates16 nsec wide pulses).

If the above settings are implemented, the Phy will automatically transmit 16ns wide pulses.

I.5.7 Generic Oscilloscope Settings

Table I-5. For Duty Cycle Distortion Measurements

0.5 nsec.

0.5 nsec.

0.5 nsec.

0.5 nsec.

16 nsec.

16 nsec.

16 nsec.

+Vout

+Vout

2

-Vout

2

-Vout

Scope Parameter Setting

Horizontal Scale ~5 ns/division, and 2 ns/division

Vertical Range -1200 mV to +1200 mV (2400 mV over the full vertical scale)

Trigger Type

Positive, Pulse Width Triggering:

~14 ns lower bound, ~18 ns upper bound

(If shorter pulses are used, the lower bound may be lowered.)

Trigger Level +400 mV

Trigger Signal 16 ns positive pulse.

Loading...

Loading...