1000BASE-T/100BASE-TX/10BASE-T Physical Layer Compliance Tests Manual

Intel Confidential 151

100Base-TX Test Procedure for the 82544 Chip

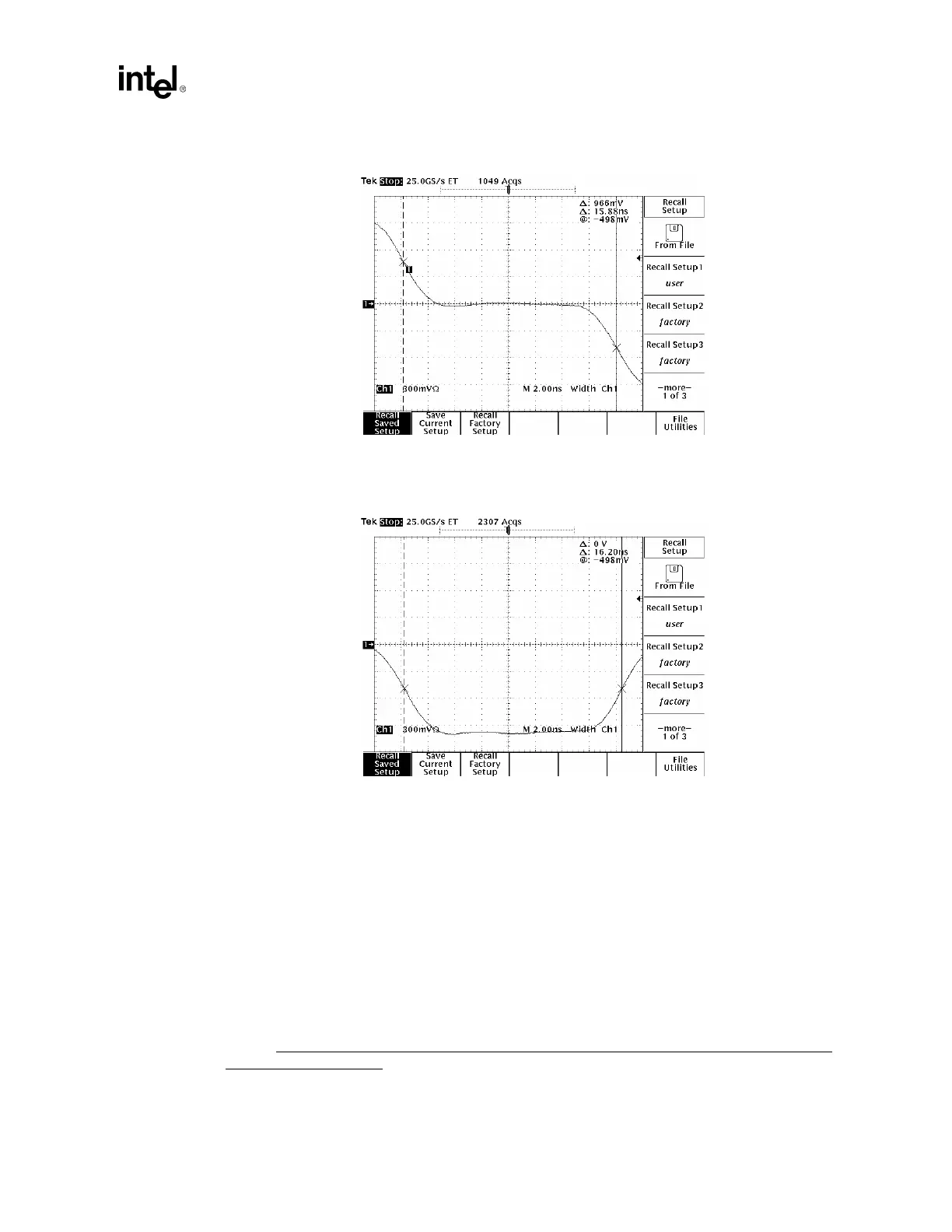

Figure I-16. MLT-3 mid-level width at 50% levels.

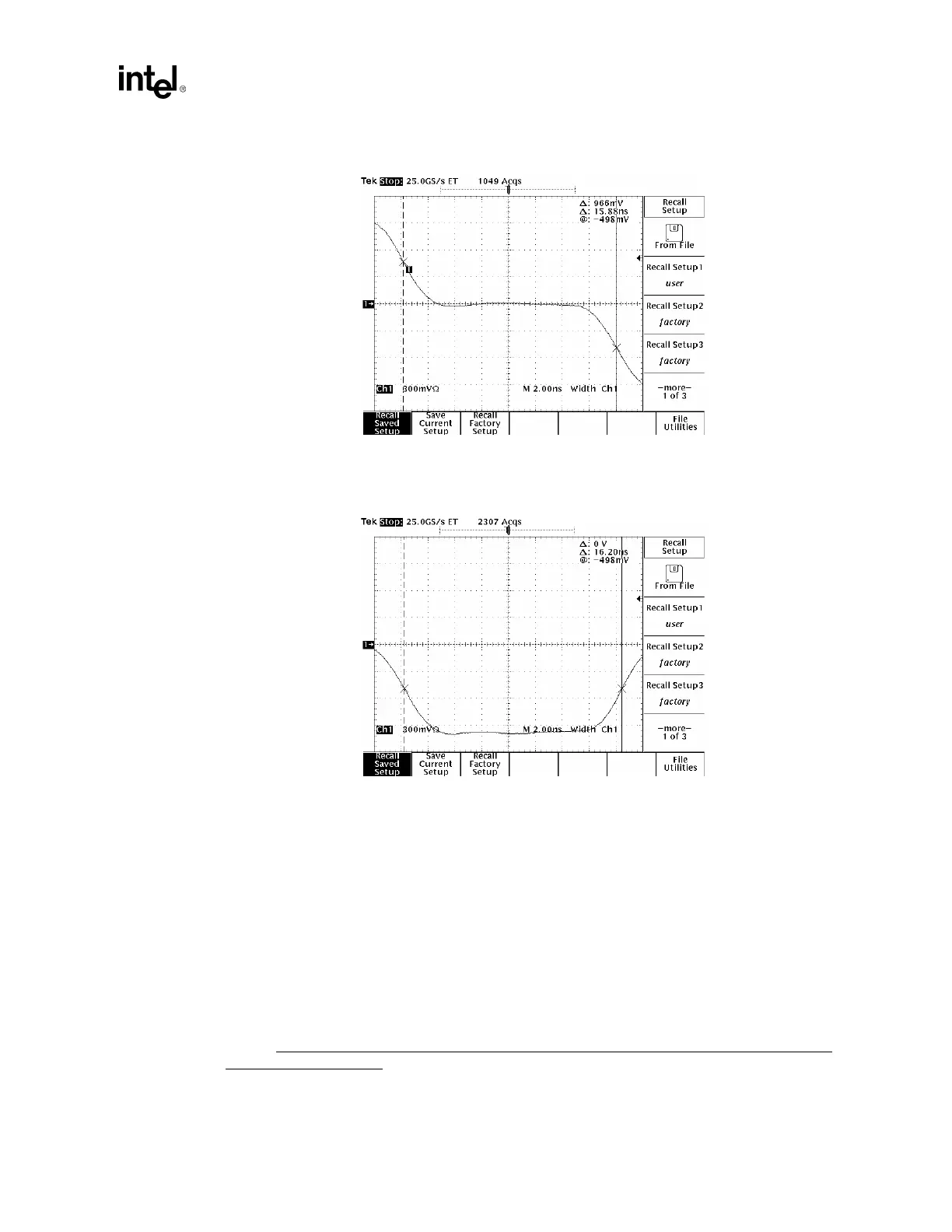

Figure I-17. Negative pulse width at 50% amplitude level

I.5.8 Duty Cycle Distortion Data

For

Figure I-14

through

Figure I-17

.

When measured between 50% voltage points on +Vout and –Vout, positive pulse widths, negative

pulse widths, and mid-level time periods must be between 15.50 nsec and 16.50 nsec.

Interpretation the ANSI TP-PMD version of this spec is somewhat confusing. The text suggests the

acceptable range for each pulse is 15.75 nsec to 16.25 nseconds, but the 9.3 illustration in the

specification clearly shows a range from 15.50 to 16.50 nsec. We believe the illustration is correct,

and it helps to explain the text within the spec, regarding a fit to a time grid with 16 nsec spacing –

That is, each edge of each pulse is allowed +/- 25 nsec deviation, so the net result is a range from

15.50 nsec to 16.50 nsec.

Loading...

Loading...