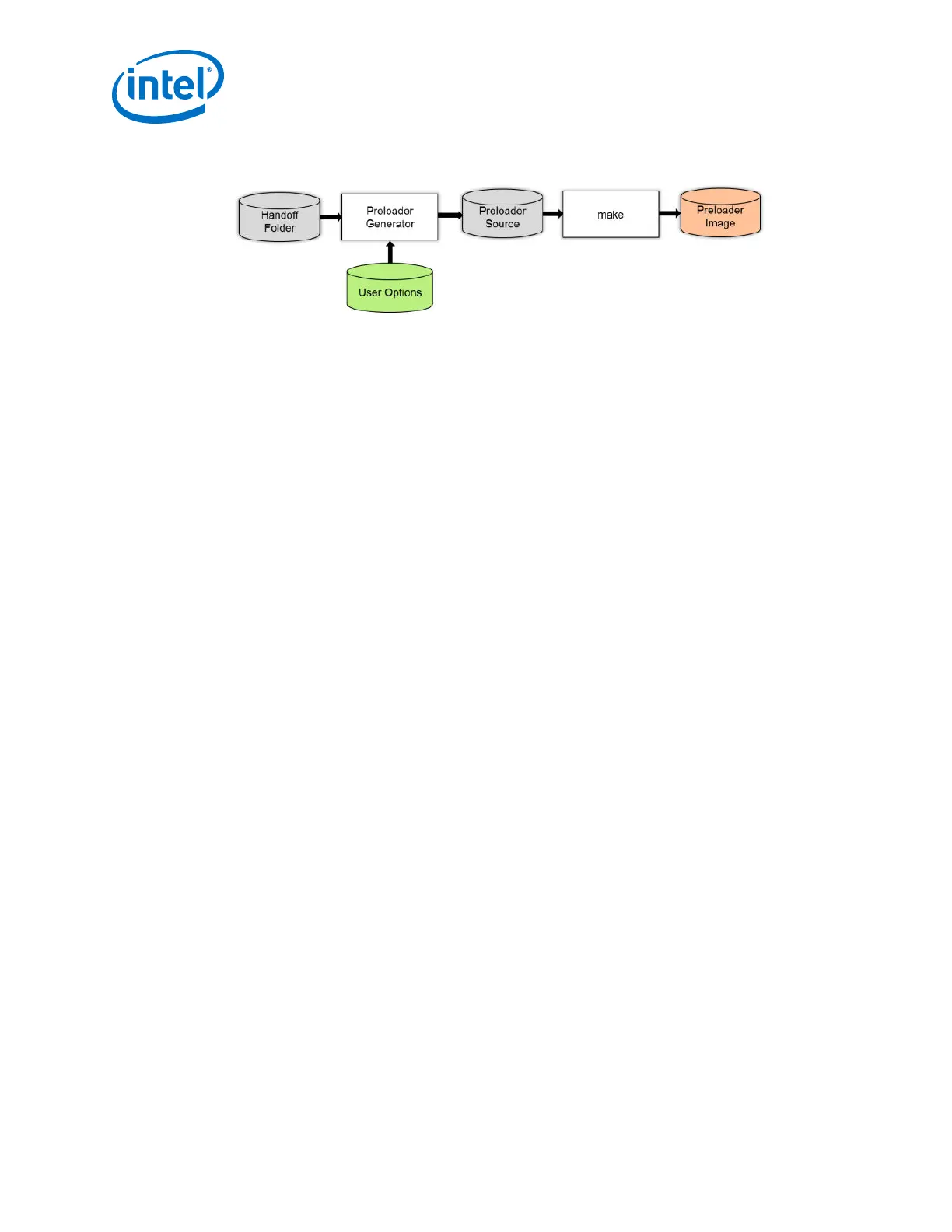

Figure 14. Preloader Build Flow

Note: It is highly recommended that Preloader is generated with bsp-editor. It is also

recommended, although not required, to build U-Boot from the same source code.

5.1.7. Selecting Software Tools for Development, Debug and Trace

Note: When using a specific Partner OS or RTOS, consult the OS vendor and the OS

documentation for any specific tools that are required. Some OS vendors also provide

a full set of tools that are recommended to be used with that OS.

Note: Familiarize yourself with the available tools for development, compilation and debug. A

list of supported tools is available at the Ecosystem tab of the Intel FPGAs page.

5.1.7.1. Select Software Build Tools

GUIDELINE: Decide which software development tools to use, and select the

tool versions.

Software development tools include compilers, assemblers, linkers, and archivers. The

Arm Development Studio 5* (DS-5*) Intel SoC FPGA Edition includes the following

software build tools:

• ARMCC Bare-metal Compiler

• Mentor Graphics CodeSourcery Lite GCC-based bare-metal Compiler

• Linux Linaro Compiler

There are also other development tools offerings from third party providers.

5.1.7.2. Select Software Debug Tools

GUIDELINE: Select software debug tools.

Arm DS-5 Intel SoC FPGA Edition includes a fully featured Eclipse-based debugging

environment. There are also other debugging tools offerings from third party providers

such as Lauterbach T32.

The debug tools require a JTAG connection to the SoC FPGA device. The connection

could be achieved in a couple of ways:

• An embedded USB-Blaster II chip could be available on-board such as on the

Cyclone V SoC / Arria V SoC Development Kit.

• External JTAG hardware may be required when using the Lauterbach T32 tools.

5. Embedded Software Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

60

Loading...

Loading...