4.5.4. SD/MMC and eMMC Card Interface Design Guidelines

GUIDELINE: Include a voltage translator if you plan on support the SD 1.8V

feature. A translator is necessary because the HPS I/O cannot change

voltage levels dynamically like the SD card.

SD cards initially operate at 3.3V, and some cards can switch to 1.8V after

initialization. In addition, some MMC cards can operate at both 1.8V as well as 3.3V.

Because the BSEL values are constant during the boot process, transceivers are

required to support level-shifting and isolation for cards that can operate at 1.8 V.

Follow the guidelines in "Voltage Switching" in the "SD/MMC Controller" chapter of the

appropriate Hard Processor System Technical Reference Manual. Some MMC cards can

operate with only 1.8V I/O operation and initial operation at 3.3V is not required. In

this situation, a level shifter is not needed.

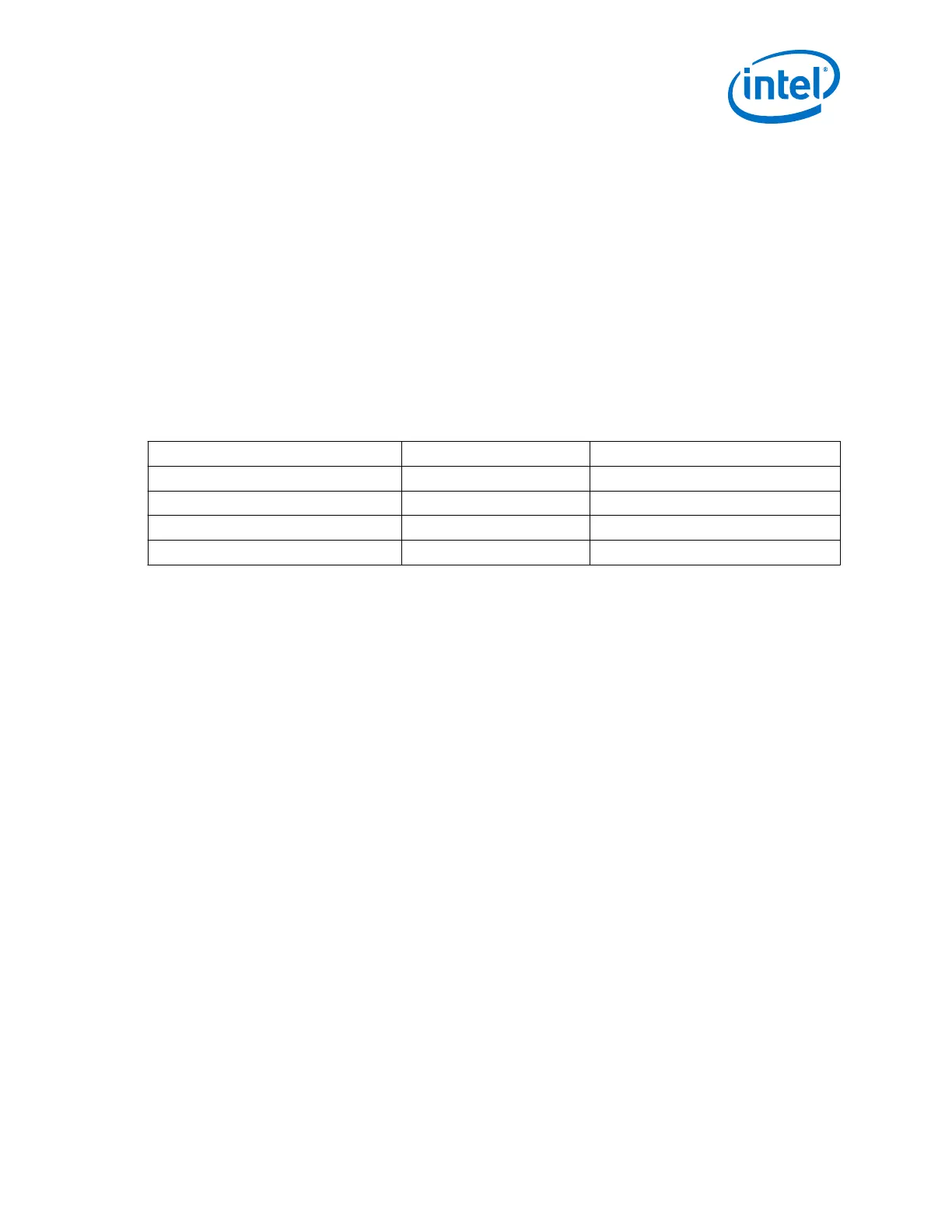

Table 8. Level Shifting Requirements

HPS I/O Bank Voltage SD Card Voltage Level Shifter Needed?

3.3V 3.3V No

3.3V 1.8V Yes

1.8V 3.3V Yes

1.8V 1.8V Yes

GUIDELINE: Ensure that timing is considered for initial ID mode and data

transfer mode as well as normal operation.

SD cards initially operate at 400 KHz maximum when they are going through the ID

process. After that there is a data transfer mode, during which the clock can operate

up to 12.5 MHz. In normal operation, the clock can operate up to 50 MHz. The Boot

ROM takes care to ensure that clocking is properly configured during ID and transfer

modes.

Refer to the "CSEL Settings for the SD/MMC Controller" table in the "Booting and

Configuration" appendix of the appropriate Hard Processor System Technical

Reference Manual.

GUIDELINE: Ensure that the SD/MMC card is reset whenever the HPS is reset.

To allow the system to boot from SD/MMC, whenever the HPS is reset, ensure that the

SD/MMC card is also reset. This ensures that the memory card is in the state expected

by the boot code.

Related Information

• Voltage Switching (Cyclone V)

Level shifting guidelines for 1.8 V SD operation in the Cyclone V HPS

• Voltage Switching (Arria V)

Level shifting guidelines for 1.8 V SD operation in the Arria V HPS

• CSEL Settings for the SD/MMC Controller

Table in the "Booting and Configuration" appendix of the Cyclone V Hard

Processor System Technical Reference Manual

4. Board Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

45

Loading...

Loading...