Technical Reference

55

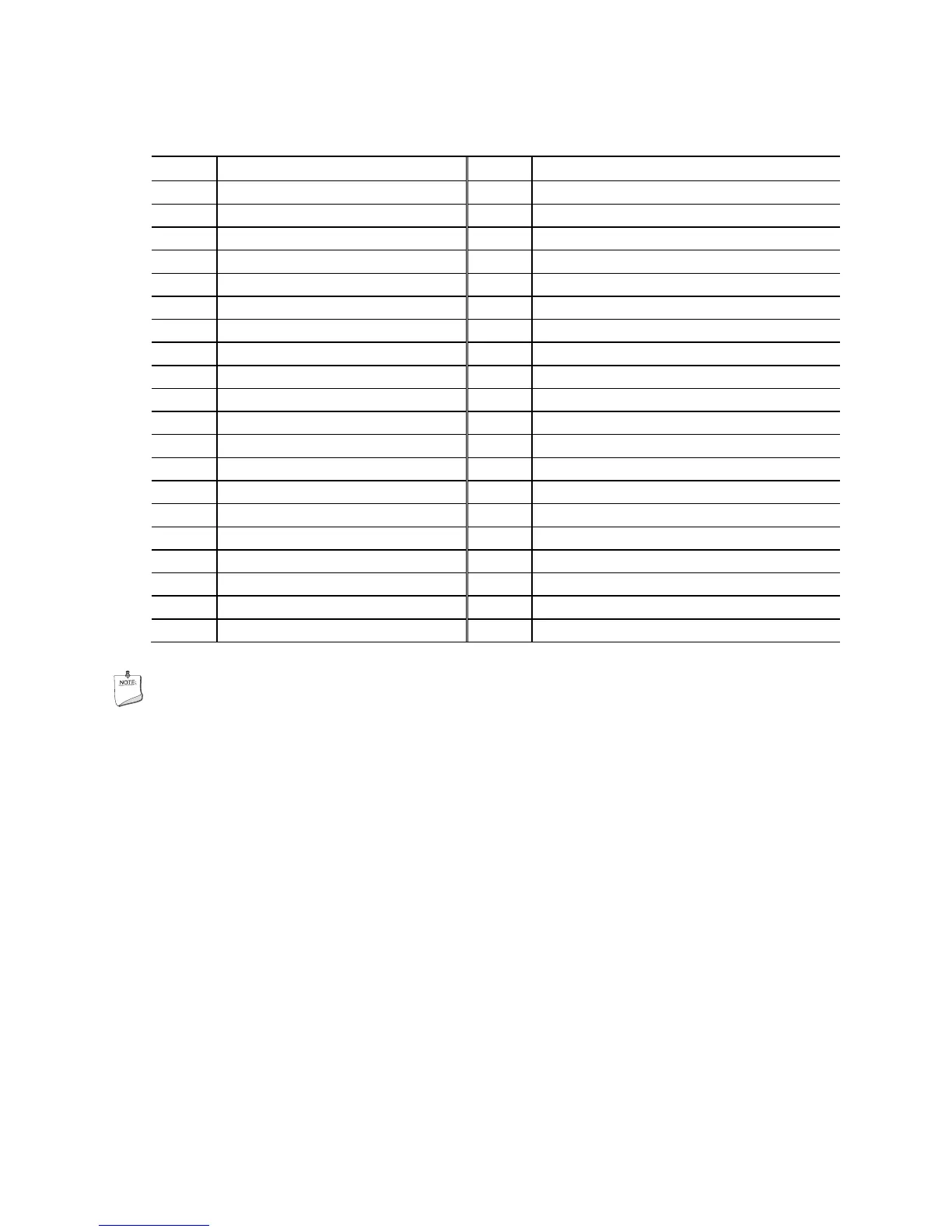

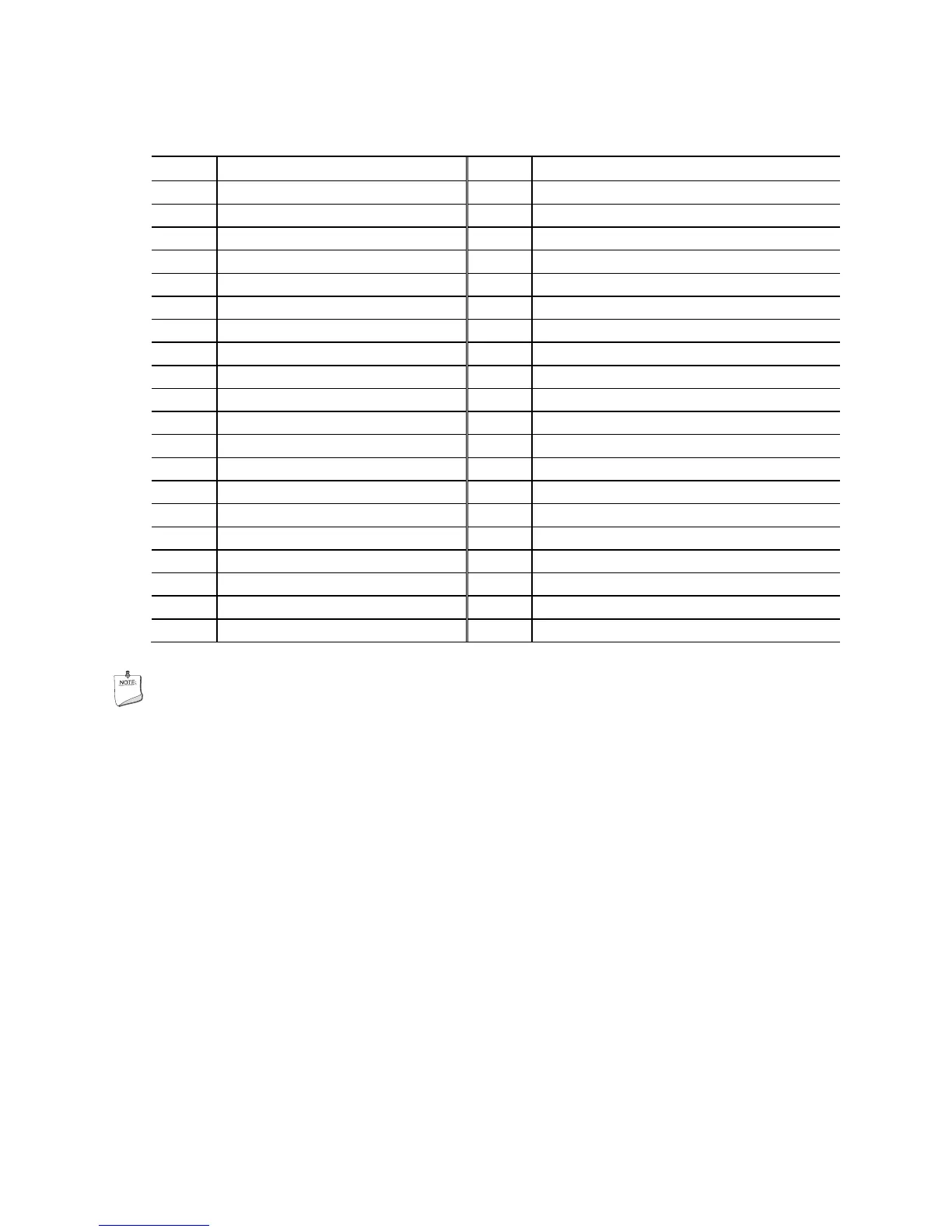

Table 30. 40-Pin LVDS Connector

Pin Signal Name Pin Signal Name

1 ODD_Lane3_P 21 N/C

2 ODD_Lane3_N 22 EDID_3.3 V

3 ODD_Lane2_P 23 LCD_GND

4 ODD_Lane2_N 24 LCD_GND

5 ODD_Lane1_P 25 LCD_GND

6 ODD_Lane1_N 26 ODD_CLK_P

7 ODD_Lane0_P 27 ODD_CLK_N

8 ODD_Lane0_N 28 BKLT_GND

9 EVEN_Lane3_P 29 BKLT_GND

10 EVEN_Lane3_N 30 BKLT_GND

11 EVEN_Lane2_P 31 EDID_CLK

12 EVEN_Lane2_N 32 BKLT_ENABLE

13 EVEN_Lane1_P 33 BKLT_PWM_DIM

14 EVEN_Lane1_N 34 EVEN_CLK_P

15 EVEN_Lane0_P 35 EVEN_CLK_N

16 EVEN_Lane0_N 36 BKLT_PWR

17 EDID_GND 37 BKLT_PWR

18 LCD_VCC 38 BKLT_PWR

19 LCD_VCC 39 N/C

20 LCD_VCC 40 EDID_DATA

NOTE

Single-channel LVDS panels must be wired to the “EVEN” channel of the LVDS

connector on initial revisions of the Intel Desktop Board DN2800MT (G23738-600 and

earlier), as opposed to the “ODD” channel expected by single-channel LVDS designs.

A future motherboard revision (G23738-800 and later) is planned to support single-

channel LVDS connectivity out of the “ODD” channel.

Intel recommends that customers planning to use single-channel LVDS panels ensure

cable wiring matches the target board revision.

Loading...

Loading...