Intel® Xeon™ Processor with 800 MHz System Bus

Datasheet 59

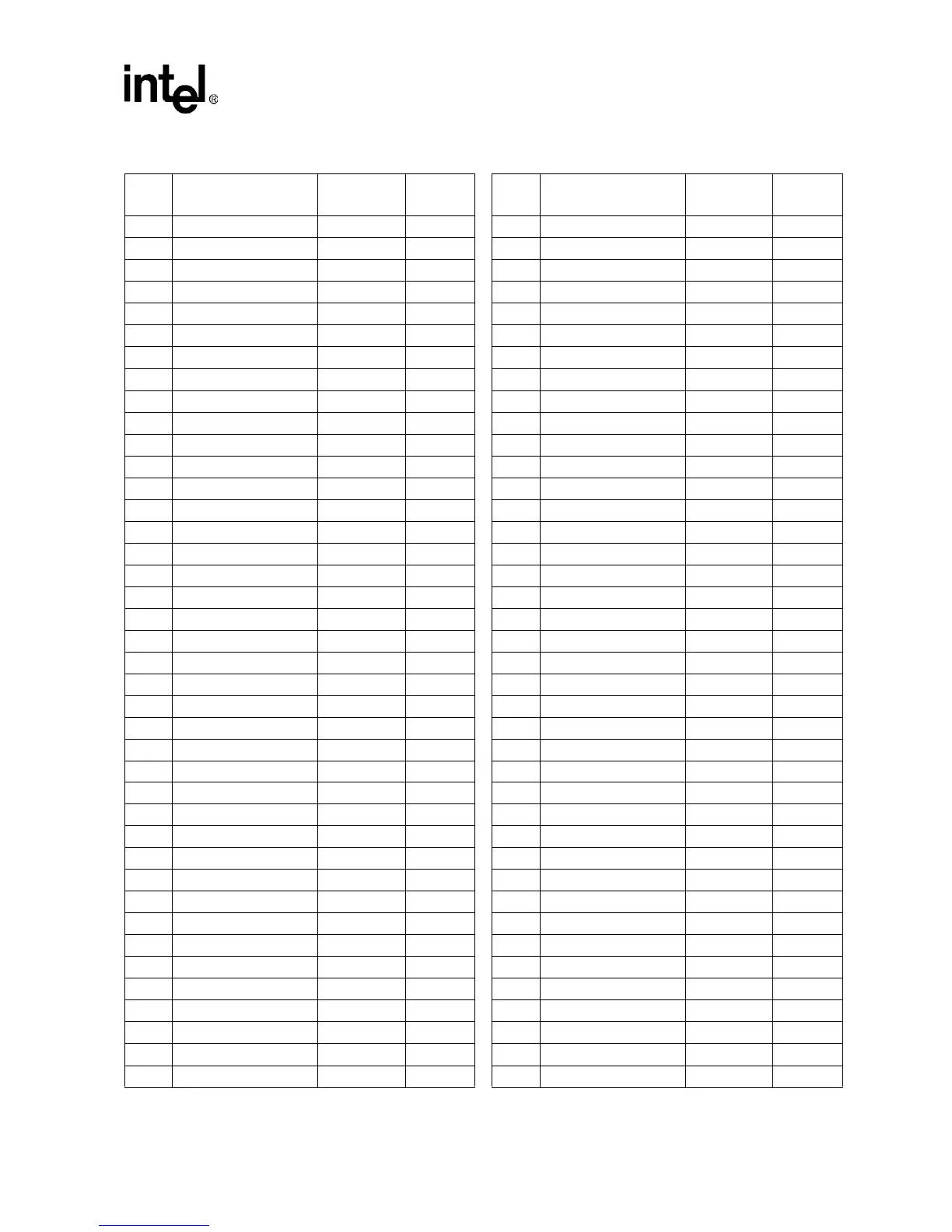

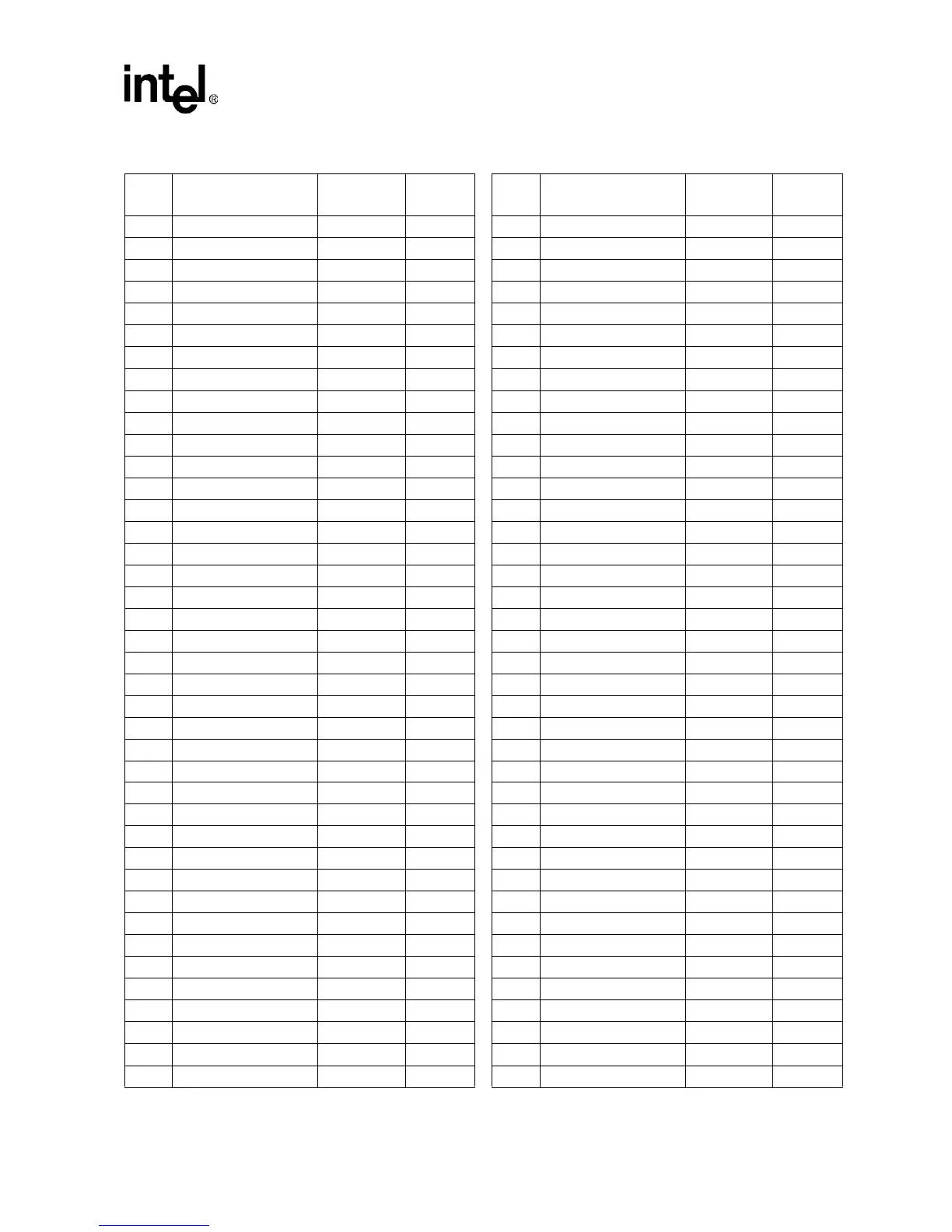

C15 A15# Source Sync I/O D24 VCC Power/Other

C16 VCC Power/Other D25 Reserved Reserved Reserved

C17 A8# Source Sync I/O D26 VSSSENSE Power/Other Output

C18 A6# Source Sync I/O D27 VSS Power/Other

C19 VSS Power/Other D28 VSS Power/Other

C20 REQ3# Source Sync I/O D29 VCC Power/Other

C21 REQ2# Source Sync I/O D30 VSS Power/Other

C22 VCC Power/Other D31 VCC Power/Other

C23 DEFER# Common Clk Input E1 VTTEN Power/Other Output

C24 TDI TAP Input E2 VCC Power/Other

C25 VSS Power/Other E3 VID1 Power/Other Output

C26 IGNNE# Async GTL+ Input E4 BPM5# Common Clk I/O

C27 SMI# Async GTL+ Input E5 IERR# Async GTL+ Output

C28 VCC Power/Other E6 VCC Power/Other

C29 VSS Power/Other E7 BPM2# Common Clk I/O

C30 VCC Power/Other E8 BPM4# Common Clk I/O

C31 VSS Power/Other E9 VSS Power/Other

D1 VCC Power/Other E10 AP0# Common Clk I/O

D2 VSS Power/Other E11 BR2#

1

Common Clk Input

D3 VID2 Power/Other Output E12 VTT Power/Other

D4 STPCLK# Async GTL+ Input E13 A28# Source Sync I/O

D5 VSS Power/Other E14 A24# Source Sync I/O

D6 INIT# Async GTL+ Input E15 VSS Power/Other

D7 MCERR# Common Clk I/O E16 COMP1 Power/Other Input

D8 VCC Power/Other E17 VSS Power/Other

D9 AP1# Common Clk I/O E18 DRDY# Common Clk I/O

D10 BR3#

1

Common Clk Input E19 TRDY# Common Clk Input

D11 VSS Power/Other E20 VCC Power/Other

D12 A29# Source Sync I/O E21 RS0# Common Clk Input

D13 A25# Source Sync I/O E22 HIT# Common Clk I/O

D14 VCC Power/Other E23 VSS Power/Other

D15 A18# Source Sync I/O E24 TCK TAP Input

D16 A17# Source Sync I/O E25 TDO TAP Output

D17 A9# Source Sync I/O E26 VCC Power/Other

D18 VCC Power/Other E27 FERR#/PBE# Async GTL+ Output

D19 ADS# Common Clk I/O E28 VCC Power/Other

D20 BR0# Common Clk I/O E29 VSS Power/Other

D21 VSS Power/Other E30 VCC Power/Other

D22 RS1# Common Clk Input E31 VSS Power/Other

D23 BPRI# Common Clk Input F1 VCC Power/Other

Table 22. Pin Listing by Pin Number (Sheet 2 of 8)

Pin

No.

Pin Name

Signal

Buffer Type

Direction

Pin

No.

Pin Name

Signal

Buffer Type

Direction

Loading...

Loading...