State of SmartFusion2 and IGLOO2 Components During Programming

UG0451 User Guide Revision 7.0 44

The following table lists the state of each ASIC block and each I/O during programming recovery.

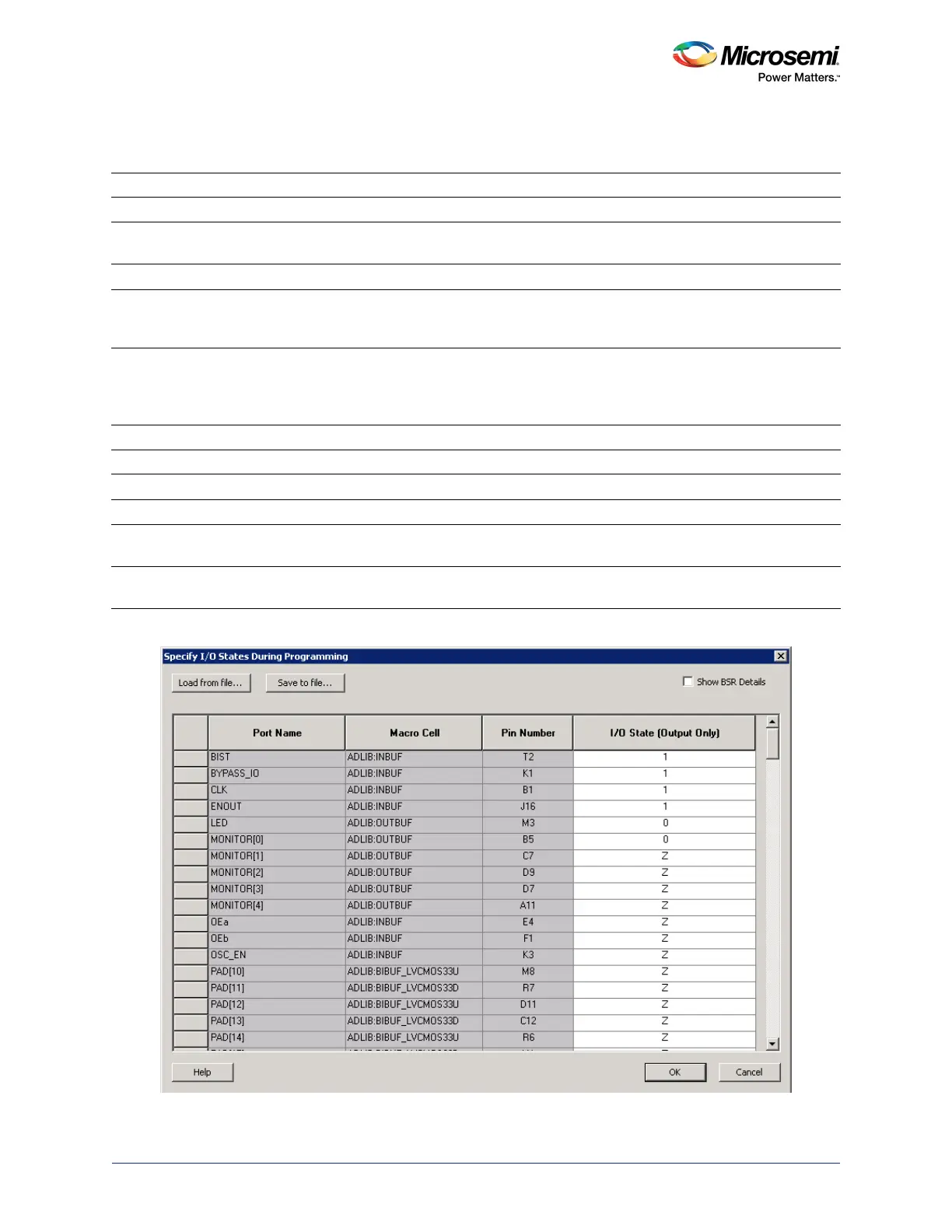

Figure 22 • I/O States During JTAG Programming

Table 27 • ASIC Block and I/O State During Programming Recovery/Auto Update

Components Programming Recovery/Auto Update

Cortex-M3 processor Held in reset.

MSS/HPMS (without

Cortex-M3)

Active during programming to permit programming access to eNVM.

MDDR controller DDR I/O calibration block held in reset.

Shared I/O

(fabric/MSS/HPMS except

SPI_0)

Tristated with weak pull up.

SPI_0 Slave select pins (SS4, SS5, SS6, and SS7) of the SPI_0 port will drive high (except

005 and 010 devices). The I/O level and drive strength are based on the previous

settings programmed into the device. All other SPI_0 I/O will be tristated with weak pull

up.

Shared I/O (fabric/MDDR) Tristated with weak pull up.

Shared I/O (fabric/FDDR) Tristated with weak pull up.

Dedicated fabric I/O Tristated with weak pull up.

SERDES I/O Unaffected by programming.

FDDR block Fabric interfaces to this block are gated off. So no transactions can occur at config APB,

AHB/AXI interfaces to fabric.

SERDESIF block Fabric interfaces to this block are gated off. So no transactions can occur at config APB,

AHB/AXI interfaces to fabric.

Loading...

Loading...