9 - 58

CHAPTER9 DEVICES

9

9.6 Index Register (Z)

9.6.1 Index register (Z)

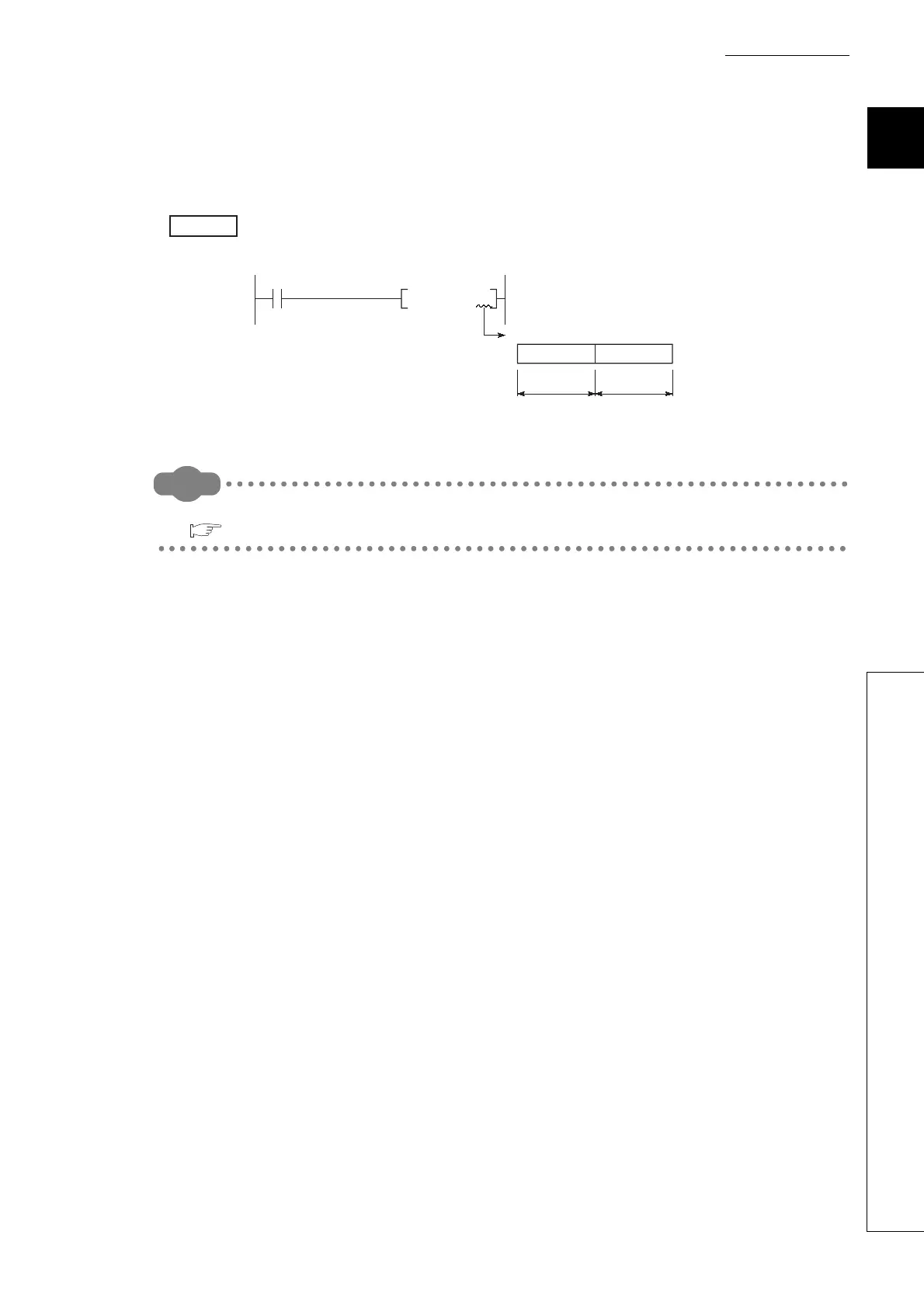

(b) When using the index register for a 32-bit instruction

The processing target is Zn and Zn+1.

The lower 16 bits correspond to the specified index register number (Zn), and the higher 16 bits correspond to

the specified index register number + 1.

When Z2 is specified in the DMOV instruction, Z2 represents the lower 16 bits and Z3

represents the higher 16 bits. (The most significant bit in a 32-bit structure is a sign bit.)

For details and precautions of index modification using the index register, refer to the following.

MELSEC-Q/L Programming Manual (Common Instruction)

Figure 9.63 Data transfer with a 32-bit instruction and storage location

Example

D0

Z2

DMOV

Z3 Z2

Processing target:

Upper 16 bits Lower 16 bits

Loading...

Loading...