MOTOROLA M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL 5- 13

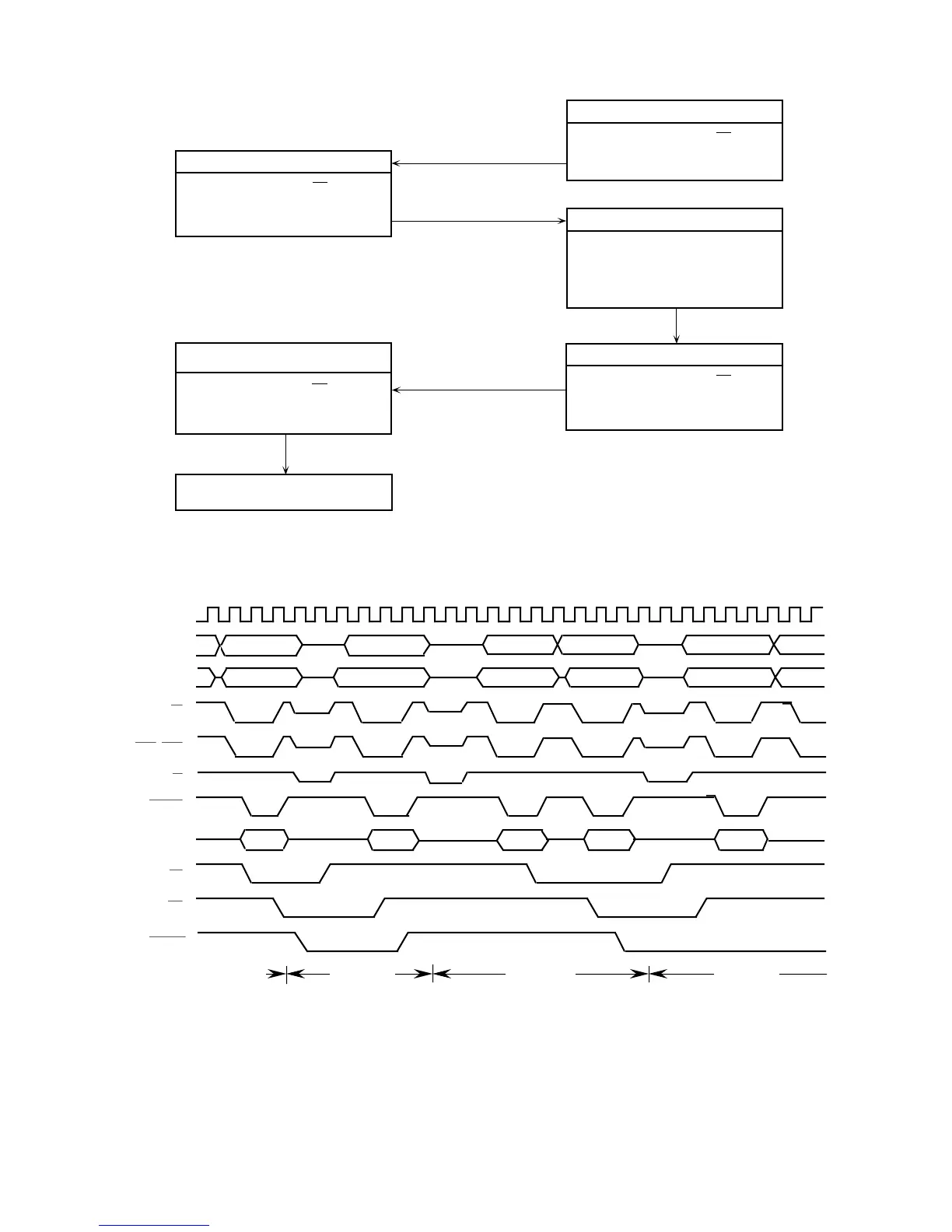

GRANT BUS ARBITRATION

REQUEST THE BUS

1) ASSERT BUS REQUEST (BR)

REQUESTING DEVICE

1) NEGATE BUS REQUEST (BR)

1) ASSERT BUS GRANT (BG)

OPERATE AS BUS MASTER

REARBITRATE OR RESUME

PROCESSOR OPERATION

RELEASE BUS MASTERSHIP

ACKNOWLEDGE RELEASE OF

BUS MASTERSHIP

1) NEGATE BUS GRANT (BG)

1) EXTERNAL ARBITRATION DETER-

MINES NEXT BUS MASTER

2) NEXT BUS MASTER WAITS FOR

CURRENT CYCLE TO COMPLETE

Figure 5-14. 2-Wire Bus Arbitration Cycle Flowchart

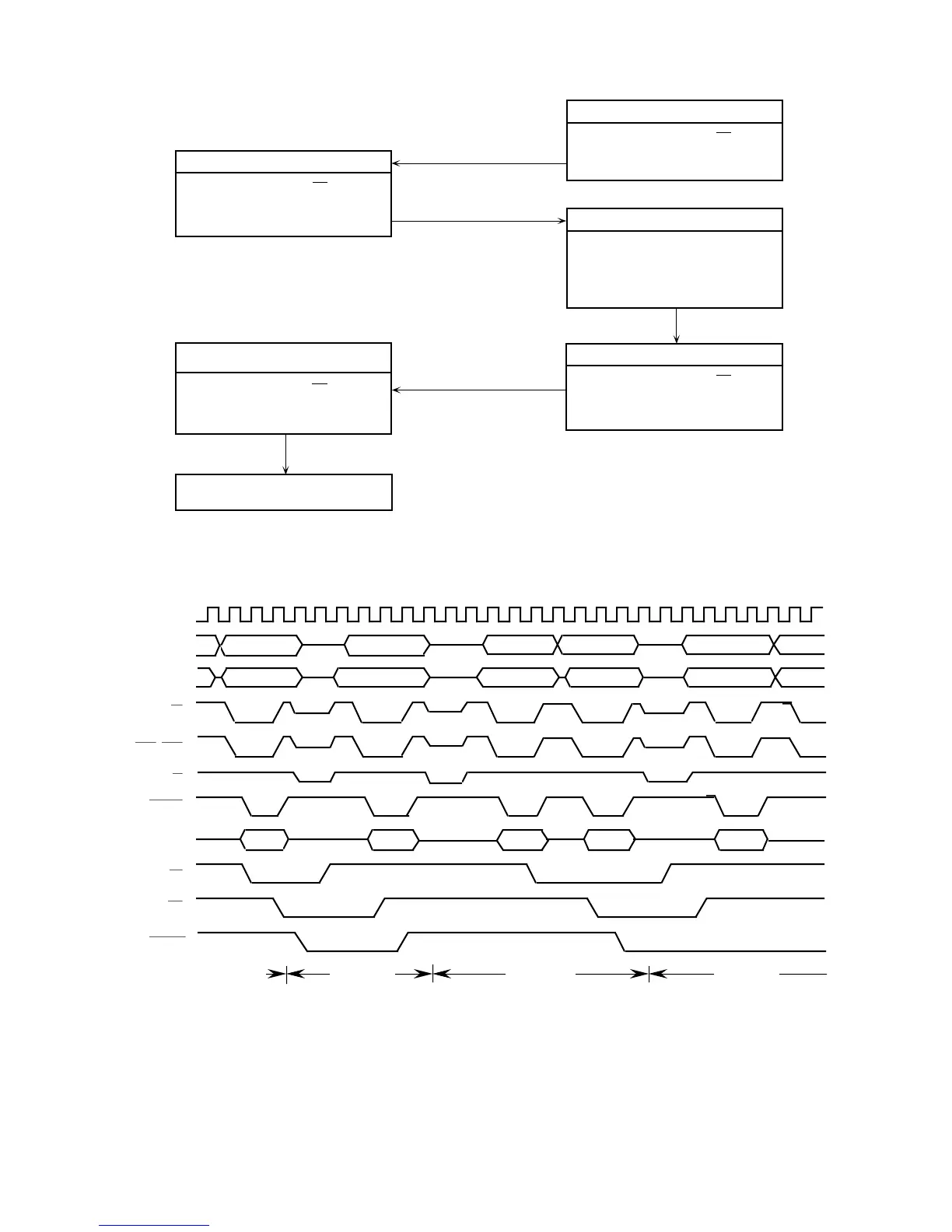

Figure 5-15. 3-Wire Bus Arbitration Timing Diagram

(Not Applicable to 48-Pin MC68008 or MC68EC000)

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...