RZ/A2M SUB Board RTK79210XXB00000BE 2. Function specifications

R20UT4398EJ0100 Rev.1.00 2-29

2018.10.11

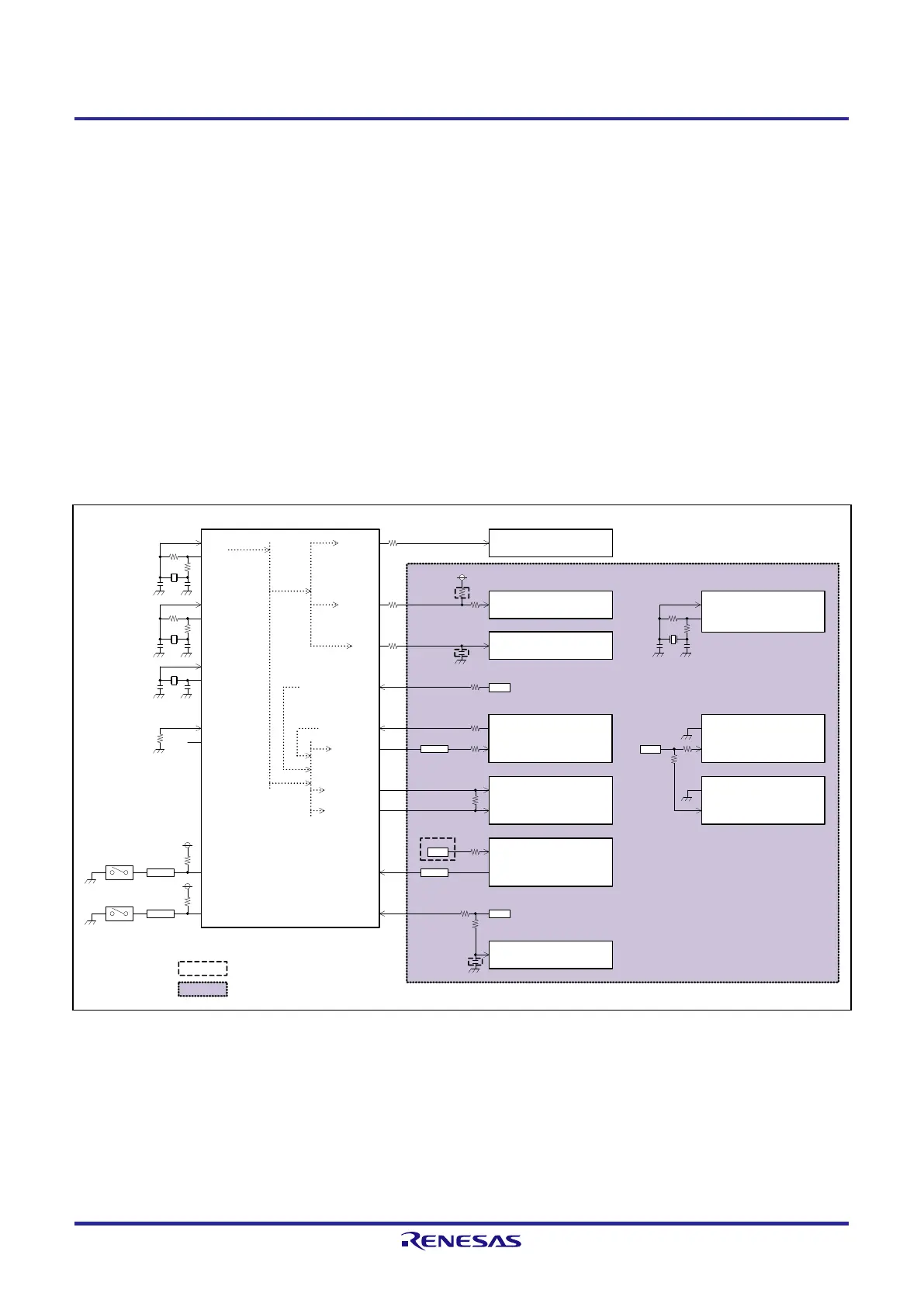

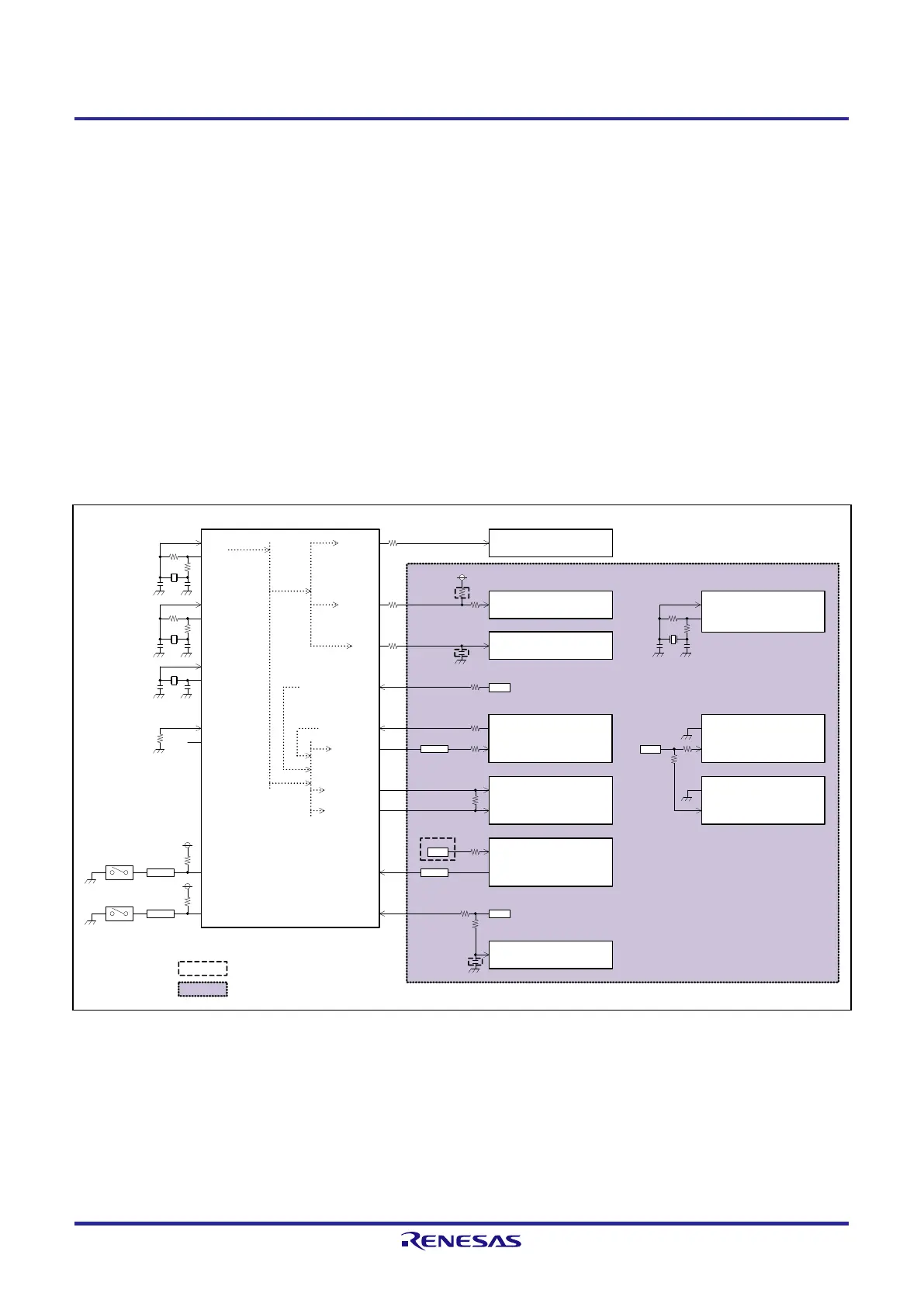

2.7 Clock Configuration

RZ/A2M receives the following three types of clock inputs from the RZ/A2M CPU board.

・RZ/A2M input clock :24 MHz

・RZ/A2M USB clock :48 MHz

・RZ/A2M RTC clock :32.768 kHz

RZ/A2M receives the following two clock inputs from RTK79210XXB00000BE.

・RZ/A2M audio clock :11.2896MHz

・RZ/A2M VDC6 clock :40MHz

Figure 2.7.1 shows clock configuration diagram, and Table 2.7.1 shows the function setting table of DIP switches

SW6-4 and SW6-6 for system setting.

Figure 2.7.1 Clock Configuration Diagram

RZ/A2M (U1)

32.768kHz

(X3)

RTC_X1

RTC_X2

24MHz

(X1)

EXTAL

XTAL

48MHz

(X2)

USB_X1

USB_X2

NC

CKIO

CLK

SDRAM(U30)

PJ_6 /

LCD0_CLK

VDC6 connector (CN15)

LCD_CLK

SD0_CLK

SD1_CLK

PJ_7 / LCD0_EXTCLK

SCLK

microSD card slot (CN1)

CLK

SD card slot (CN10)

PL_1 / MD_CLK

L=10~12MHz, H=20~24MHz

PL_0 / MD_CLKS

L=SSCG:OFF, H=SSCG:ON

CLK

P6_4 / AUDIO_CLK

CLK

11.2896MHz

Socket(X1)

MCLK

Audio CODEC(U21)

DV_CLKP7_2 / DV0_CLK

CLK+

CLK-

LVDS connector (CN14)

P4_6 /

TXCLKOUTP

P4_7 /

TXCLKOUTM

Socket(X5)

REFCLK

CMOS camera connector (CN17)

CLK

Socket(X6)

Ethernet PHY1(U27)

CKXTAL2

Ethernet PHY2(U28)

CKXTAL2

CKXTAL1

CKXTAL1

CLK

50MHz

(X4)

AUDIO_X1

AUDIO_X2

X1

RL78(U23)

X2

12MHz

(X3)

3.3V

VIO_CLKP6_1 / VIO_CLK

Note: Red text indicates a function used.

:Indicates a function not implemented.

:Indicates a SUB board.

MUX

MUX

DIP

SW1-2

3.3V

DIP

SW1-1

3.3V

OFF

MUX

MUX

40MHz

Loading...

Loading...