S5-100U Interrupt Processing

10 Interrupt Processing, for CPU 103 Version

8MA02 and Higher

Interrupt-driven program processing starts when a signal from the CPU causes the programmable

controller to interrupt cyclic or time-controlled program scanning in order to process a specific

program. Once this program has been scanned, the CPU returns to the point of interruption in the

cyclic or time-controlled program and resumes processing at that point.

Prerequisites for Interrupt-Driven Program Processing

Interrupt-driven program processing is possible only if the following conditions are met:

• The bus unit with interrupt capability is directly adjacent to the CPU (slots 0 and 1).

• Four-channel digital input modules or comparator modules must be mounted on the bus unit to

transfer process interrupts.

- You may plug other modules in, but these modules will have no interrupt handling capability.

• The programmable controller is in the Power ON state and in the RUN operating mode.

• Interrupt processing is not disabled by an IA operation in your program. See section 8.2.8.

• OB2 has been programmed.

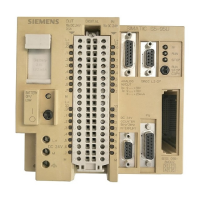

Figure 10-1. Possible Configuration of the Programmable Controller with Bus Units

Having Interrupt Capability

°

°

°

°

°

°

°

°

8

DI

°

°

°

°

4

DI

°

°

°

°

Slot 0 1 2 3

°

°

°

°

°

°

°

°

8

DI

4

DI

CPU

Bus unit with interrupt capability (but

acts only like a “normal” bus unit)

Interrupts are handled

only by this module

Bus unit with interrupt capability

10.1 Interrupt Processing with OB2, for CPU 103 Version 8MA02 and

Higher

For interrupt-driven processing, OB2 must have been programmed. OB2 is called up by a process

interrupt and interrupts in turn the cyclic or time-controlled program scanning. Other blocks can be

called from OB2. After the interrupt-driven program has been processed, the CPU resumes cyclic

or time-controlled program scanning.

EWA 4NEB 812 6120-02

10-1

Loading...

Loading...