S5-100U Technical Description

Table 2-1 gives information about the number and retentive characteristics (the internal memory

contents are retained/are not retained) of these timers, counters, and flags.

Table 2-1. Retentive and Non-Retentive Operands

Operand

Retentive

CPU 100 to 103

Non-Retentive

CPU 100 CPU 102 CPU 103

Flags 0.0 to 63.7 64.0 to 127.7 64.0 to 127.7 64.0 to 255.7

Counters 0 to 7 8 to 15 8 to 31 8 to 127

Timers

0 to 15 0 to 31 0 to 127

Arithmetic Unit

The arithmetic unit (ALU) consists of two accumulators, ACCU 1 and 2. The accumulators can

process byte and word operations.

Figure 2-3. Example of an Arithmetic Logic Unit’s Mode of Operation

Load

information

from the PII.

Transfer

information

to the PIQ.

Process

information

in ACCU 1 and ACCU 2.

Accumulator Design

Figure 2-4. Accumulator Design

ACCU 2 ACCU 1

Low byteHigh byte

15 8 7 0

15

8 7

0

High byte Low byte

Processor

According to the control program, the processor calls statements in the program memory in

sequence and executes them. It processes the information from the PII and takes into consideration

the values of internal timers and counters as well as the signal states of internal flags.

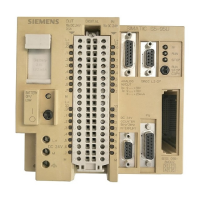

External I/O Bus

The I/O bus is the electrical connection for all signals that are exchanged between the CPU and the

S5-100U modules in a programmable controller.

EWA 4NEB 812 6120-02

2-5

Loading...

Loading...