90

HCD-SR4W

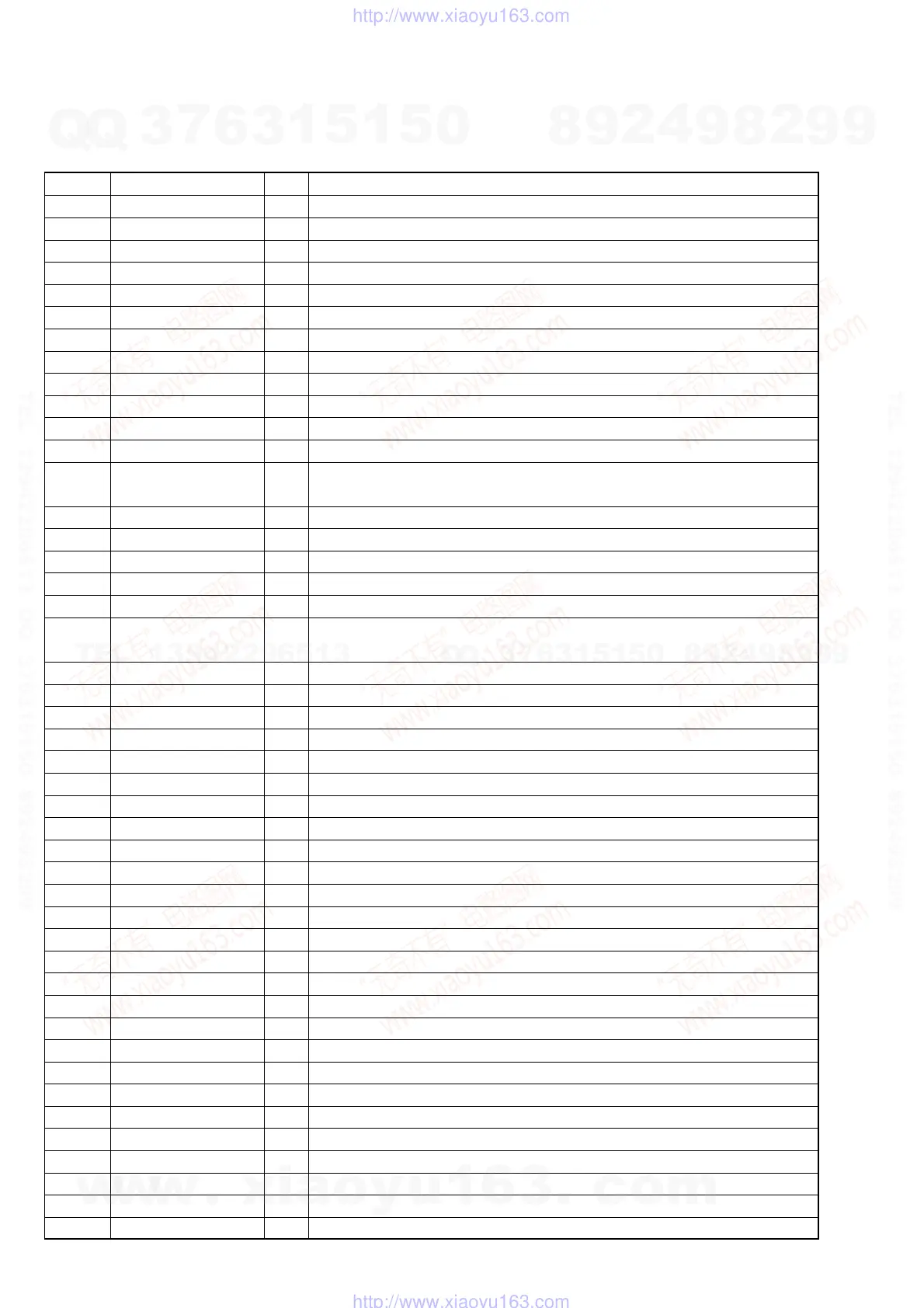

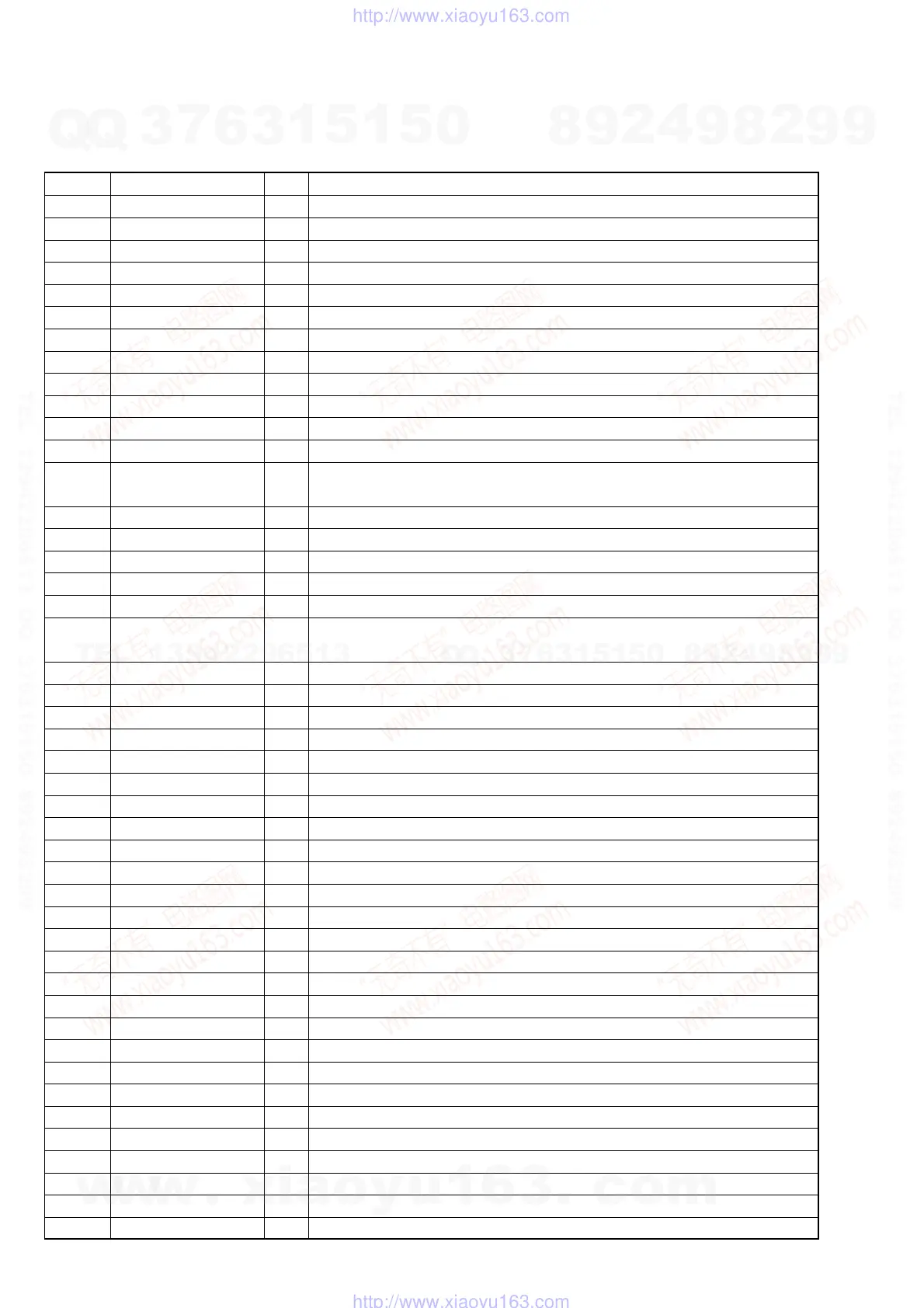

DMB08 BOARD IC607 CXD9618BQ (AUDIO DIGITAL SIGNAL PROCESSOR)

Pin No. Pin Name I/O Description

1 VSS — Ground terminal

2 XRST I Reset signal input from the system controller “L”: reset

3 EXTIN I Master clock signal input terminal Not used

4 FS2 I Sampling frequency selection signal input terminal Not used

5 VDDI — Power supply terminal (+2.6V)

6 FS1 I Sampling frequency selection signal input terminal Not used

7 PLOCK O Internal PLL lock signal output terminal Not used

8 VSS — Ground terminal

9 MCLK1 I System clock signal input terminal (13.5 MHz)

10 VDDI — Power supply terminal (+2.6V)

11 VSS — Ground terminal

12 MCLK2 O System clock signal output terminal (13.5 MHz)

13 MS I

Master/slave selection signal input terminal

“L”: slave, “H”: master (fixed at “L” in this set)

14 SCKOUT O Internal system clock signal output to the D/A converter and stream processor

15 LRCKI1 I L/R sampling clock signal (44.1 kHz) input from the digital audio processor

16 VDDE — Power supply terminal (+3.3V)

17 BCKI1 I Bit clock signal (2.8224 MHz) input from the digital audio processor

18 SDI1 I Front L-ch and R-ch audio serial data input from the digital audio processor

19 LRCKO O

L/R sampling clock signal (44.1 kHz) output to the D/A converter and stream

processor

20 BCKO O Bit clock signal (2.8224 MHz) output to the D/A converter and stream processor

21 VSS — Ground terminal

22 KFSIO I Audio clock signal (11.2896 MHz) input from the digital audio processor

23 SDO1 O Front L-ch and R-ch audio serial data output to the stream processor

24 SDO2 O Center and woofer audio serial data output to the stream processor

25 SDO3 O Rear L-ch and R-ch audio serial data output to the stream processor

26 SDO4 O Audio serial data output to the D/A converter

27 SPDIF O S/PDIF signal output terminal Not used

28 LRCKI2 I L/R sampling clock signal (44.1 kHz) input from the A/D converter

29 BCKI2 I Bit clock signal (2.8224 MHz) input from the A/D converter

30 SDI2 I Center and woofer audio serial data input from the digital audio processor

31 VSS — Ground terminal

32 HACN O Acknowledge signal output to the system controller

33 HDIN I Write data input from the system controller

34 HCLK I Clock signal input from the system controller

35 HDOUT O Read data output to the system controller

36 HCS I Chip select signal input from the system controller

37 SDCLK O Clock signal output terminal Not used

38 CLKEN O Clock enable signal output terminal Not used

39 RAS O Row address strobe signal output terminal Not used

40 VDDI — Power supply terminal (+2.6V)

41 VSS — Ground terminal

42 CAS O Column address strobe signal output terminal Not used

43 DQM/OE0 O Output terminal of data input/output mask Not used

44 CS0 O Chip select signal output to the S-RAM

45 WE0 O Write enable signal output to the S-RAM

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...