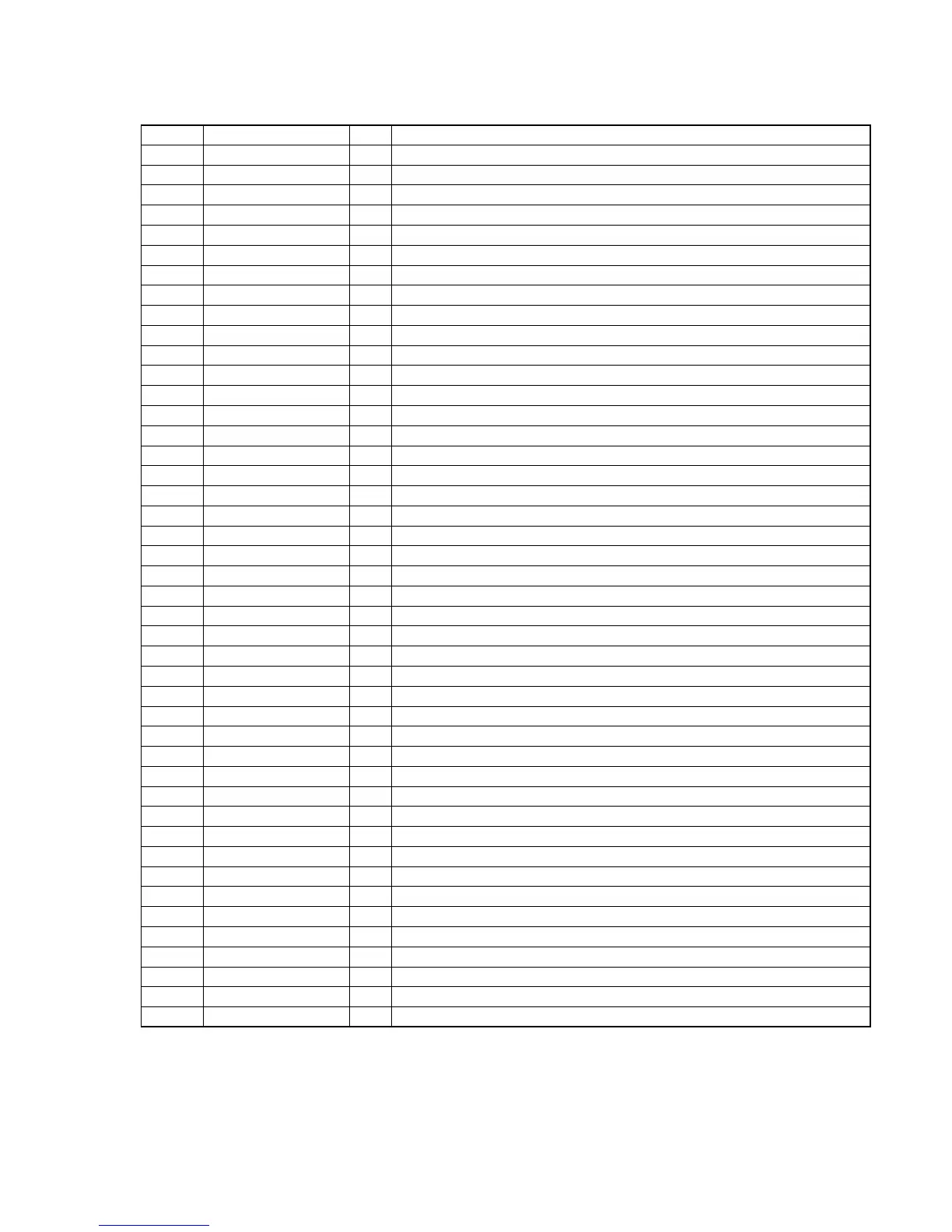

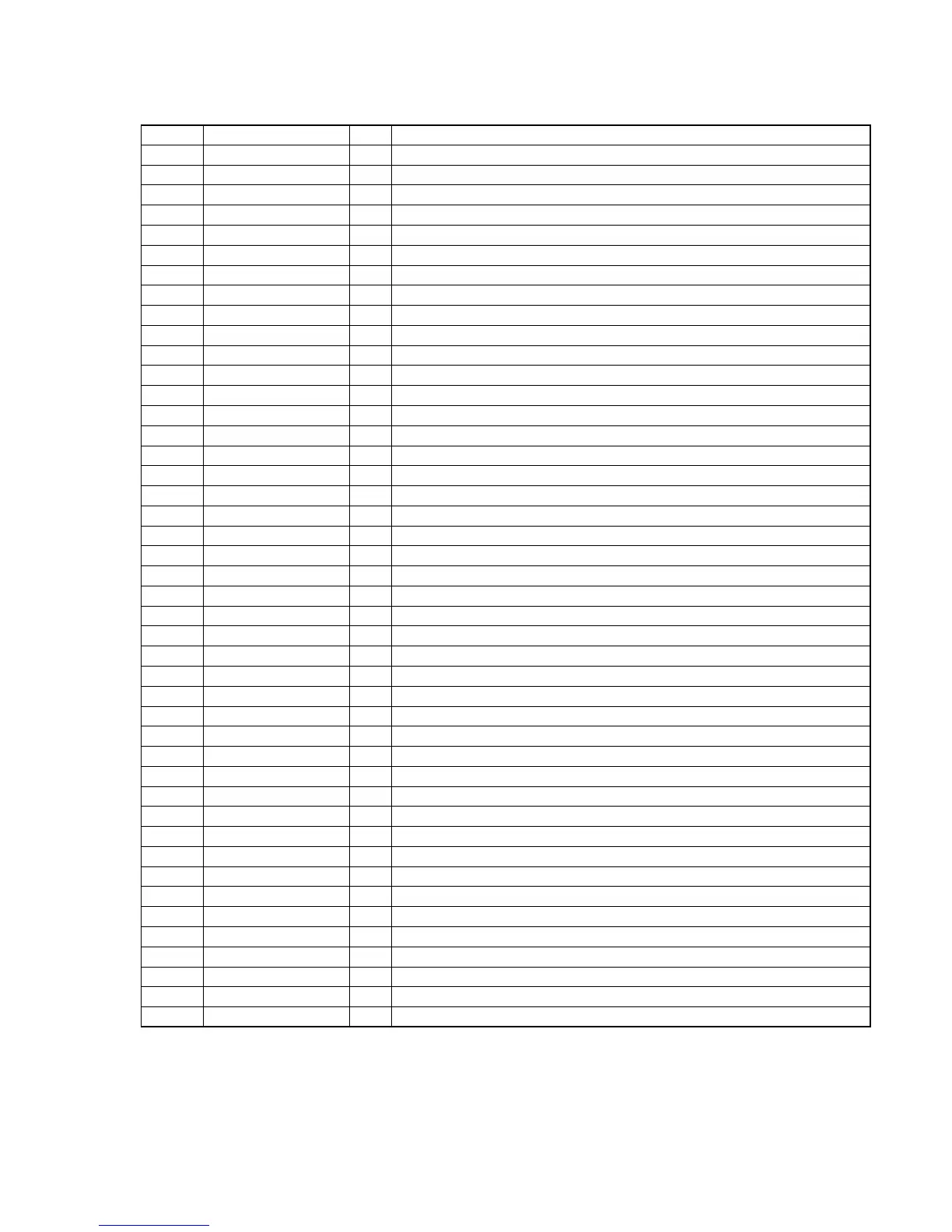

49

• IC502 MPEG DECODER, MECHANISM CONTROL (M30624MCA-A34FP) (VIDEO Board (1/3))

Pin No. Pin Name I/O Function

1 SENSE I Internal state (SENSE) monitor input (IC101)

2 SENSE CLK O Serial data reading clock output (IC101)

3 RESOLUTION O Serial data output (IC101)

4 CROMA LEVEL O Lach output (IC101)

5 DSP CLK O Serial data clock output (IC101)

6 TSENS I Not used

7 REMOTE IN I Not used

8 BYTE I External bus width change input (Connected to ground)

9 CNVSS – Ground

10 DSP MUTE O Mute output (IC101) “H” : mute

11 CTRL1 (L : DOUBLE) O Double change output (IC101) “L” : double

12 XRESET I System reset input “L” : reset

13 XOUT O Main clock output (10MHz)

14 VSS – Ground

15 XIN I Main clock input (10MHz)

16 VCC – +5V power supply

17 NMI I Requests mask disable interruption input (Connected to +5V)

18 SCOR I Subcode sync input (IC101)

19 D SENS I Not used

20 CL680 INT I Video CD interruption input (IC505)

21 CL680 HSEL O Video CD select data of the host MPU (IC505)

22 DF LATCH O Digital filter latch output (IC509)

23 CL680 HRDY I Ready signal input for communication to the host MPU (IC505)

24 680 RESET O Video CD reset output (IC505) “L” : reset

25 H. SYNC IN I H. sync signal input

26 BGP I BGP output

27 LPH O Double control output (IC101) “H” : double

28 LD ON O Laser diode ON/OFF output

29 IIC. CLK I/O IIC clock input from master control

30 IIC. DATA I/O IIC data input from master control

31 DATA1O O Serial 1 data output (IC505, 509)

32 DATA1I I Serial 1 data input (IC505, 509)

33 CLK1 O Serial 1 clock output

34 RTS1 O

35 XVLEVEL. DOWN O Fix the video signal output level output

36 SUBQ DATA I Serial 2 data input for subcode sync reading

37 SUBQ CLK I Serial 2 clock input for subcode sync reading

38 P. ON I Not used

39 BUS XRDY I Not used

40 BUS I Not used

41 BUS XHOLD I Not used

42, 43 BUS I Not used

44 BUS XRD I Model selection input “L” : chinese model, “H” : except chinese model

45 V. SYNC I V sync signal input

Loading...

Loading...