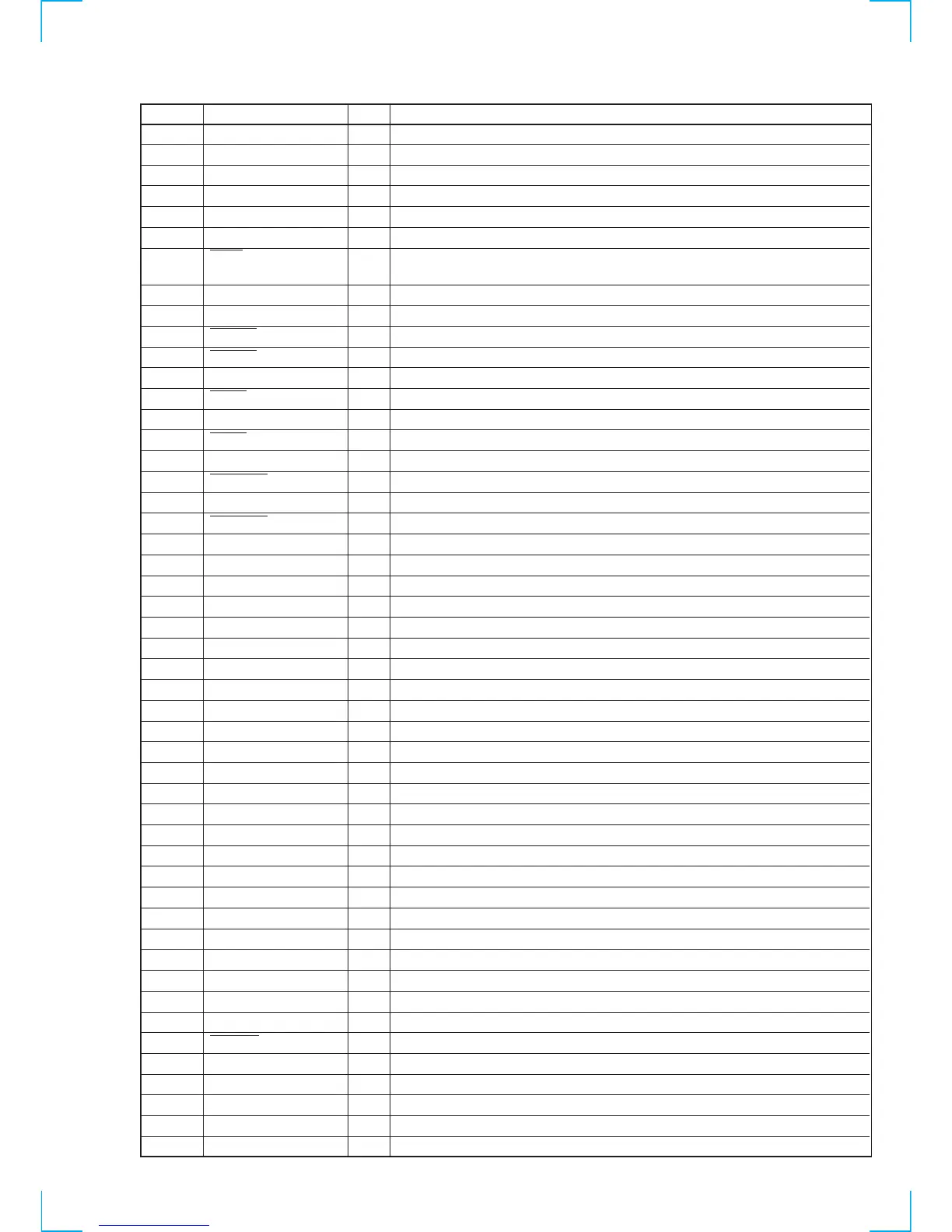

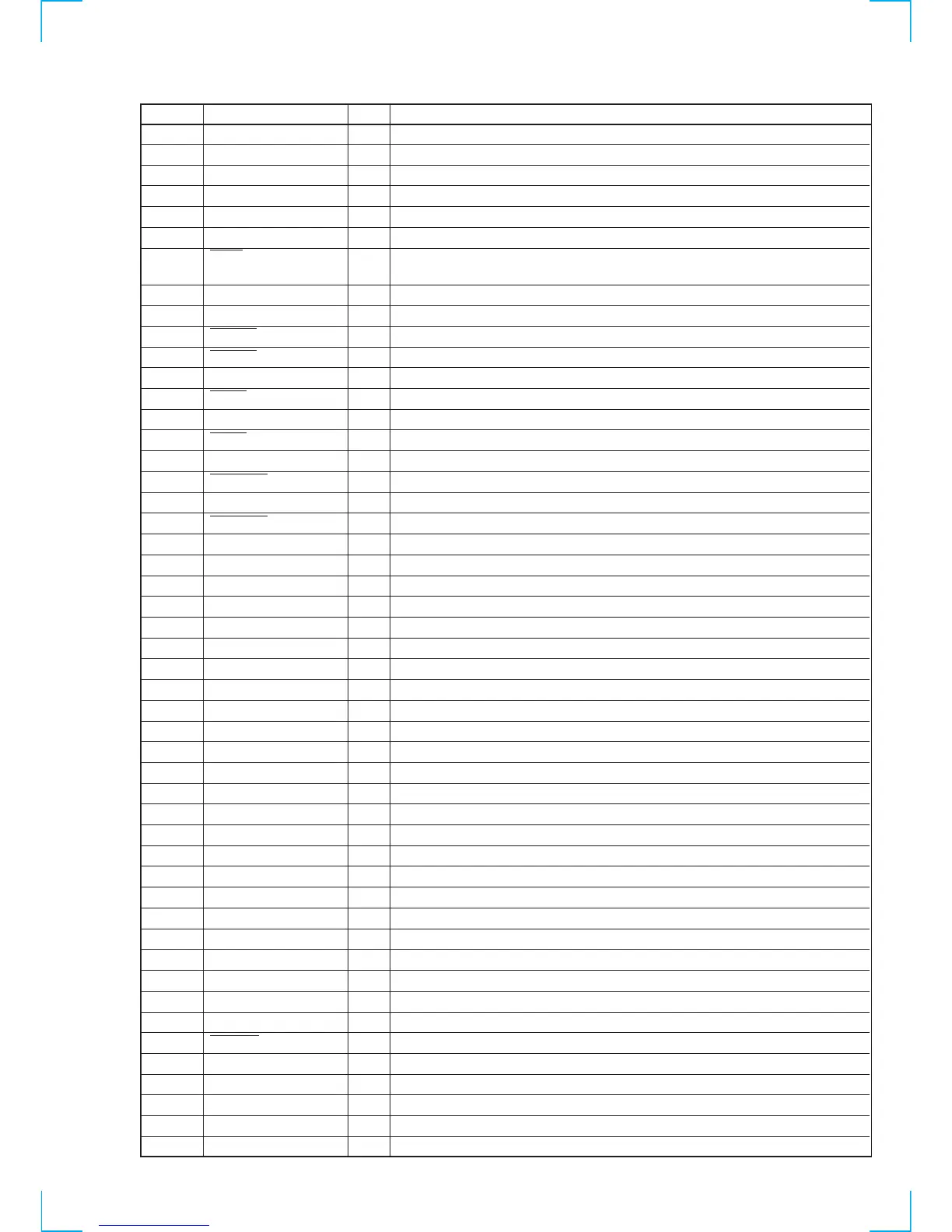

57

76 MDATA [15:0] I/O Memory address.

77 VSS — Ground for core logic and I/O signals.

78 MDATA [15:0] I/O Memory address.

79 LDQM O SDRAM LDQM.

80 UDQM O SDRAM UDQM.

81 VDD — 3.3-V supply voltage for core logic and I/O signals.

82 MWE O SDRAM/EDO write enable. Decoder asserts active LOW to request a write operation

to the SDRAM array.

83 VSS — Ground for core logic and I/O signals.

84 SD-CLK O SDRAM system clock.

85 SD-CAS O Active LOW SDRAM column address.

86 SD-RAS O Active LOW SDRAM row address.

87 VDD — 3.3-V supply voltage for core logic and I/O signals.

88 SD-CS [1:0] O Active LOW SDRAM bank select.

89 VSS — Ground for core logic and I/O signals.

90 SD-CS [1:0] O Active LOW SDRAM bank select.

91 VDD — 3.3-V supply voltage for core logic and I/O signals.

92 EDO-CAS O Active LOW EDO DRAM column address strobe.

93 VSS — Ground for core logic and I/O signals.

94 EDO-RAS O Active LOW EDO DRAM row address strobe.

95 VDD — 3.3-V supply voltage for core logic and I/O signals.

96 MADDR [20:0] O Memory address.

97 VSS — Ground for core logic and I/O signals.

98 to 100 MADDR [20:0] O Memory address.

101 VDD — 3.3-V supply voltage for core logic and I/O signals.

102 MADDR [20:0] O Memory address.

103 VSS — Ground for core logic and I/O signals.

104 to 106 MADDR [20:0] O Memory address.

107 VDD — 3.3-V supply voltage for core logic and I/O signals.

108 MADDR [20:0] O Memory address.

109 VSS — Ground for core logic and I/O signals.

110 to 112 MADDR [20:0] O Memory address.

113 VDD — 3.3-V supply voltage for core logic and I/O signals.

114 MADDR [20:0] O Memory address.

115 VSS — Ground for core logic and I/O signals.

116 MADDR [20:0] O Memory address.

117 VDD — 3.3-V supply voltage for core logic and I/O signals.

118 MADDR [20:0] O Memory address.

119 VSS — Ground for core logic and I/O signals.

120 to 122 MADDR [20:0] O Memory address.

123 VDD — 3.3-V supply voltage for core logic and I/O signals.

124 MADDR [20:0] O Memory address.

125 VSS — Ground for core logic and I/O signals.

126, 127 MADDR [20:0] O Memory address.

128 ROM-CS O ROM chip select. Open drain signal, must be pulled-up to 3.3 volts.

129 PIO [10:0] I/O Programmable I/O pins.

133 PIO [10:0] I/O Programmable I/O pins.

134 VDD — 3.3-V supply voltage for core logic and I/O signals.

136 VSS — Ground for core logic and I/O signals.

138 PIO [10:0] I/O Programmable I/O pins.

Pin No.

Pin Name

I/O Function

Loading...

Loading...