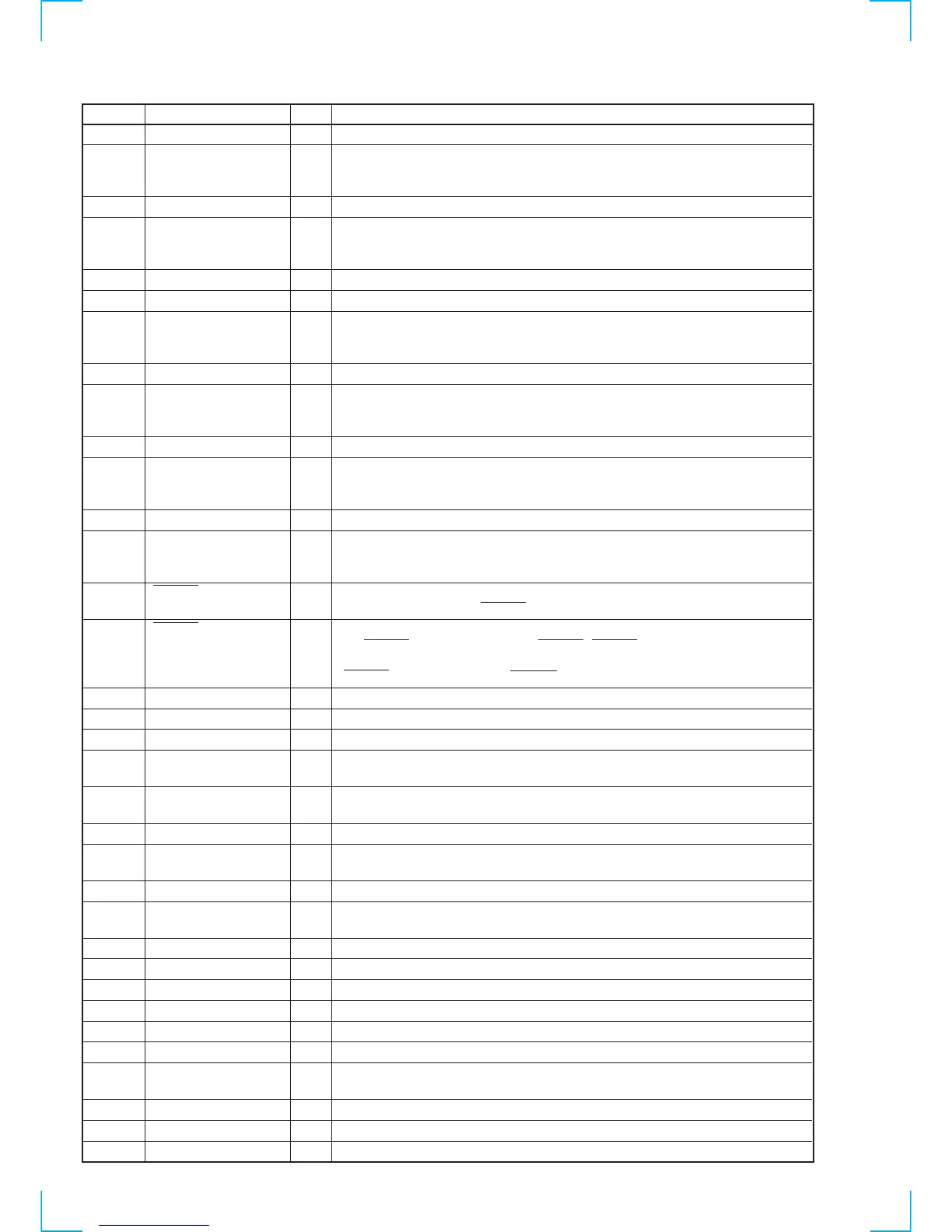

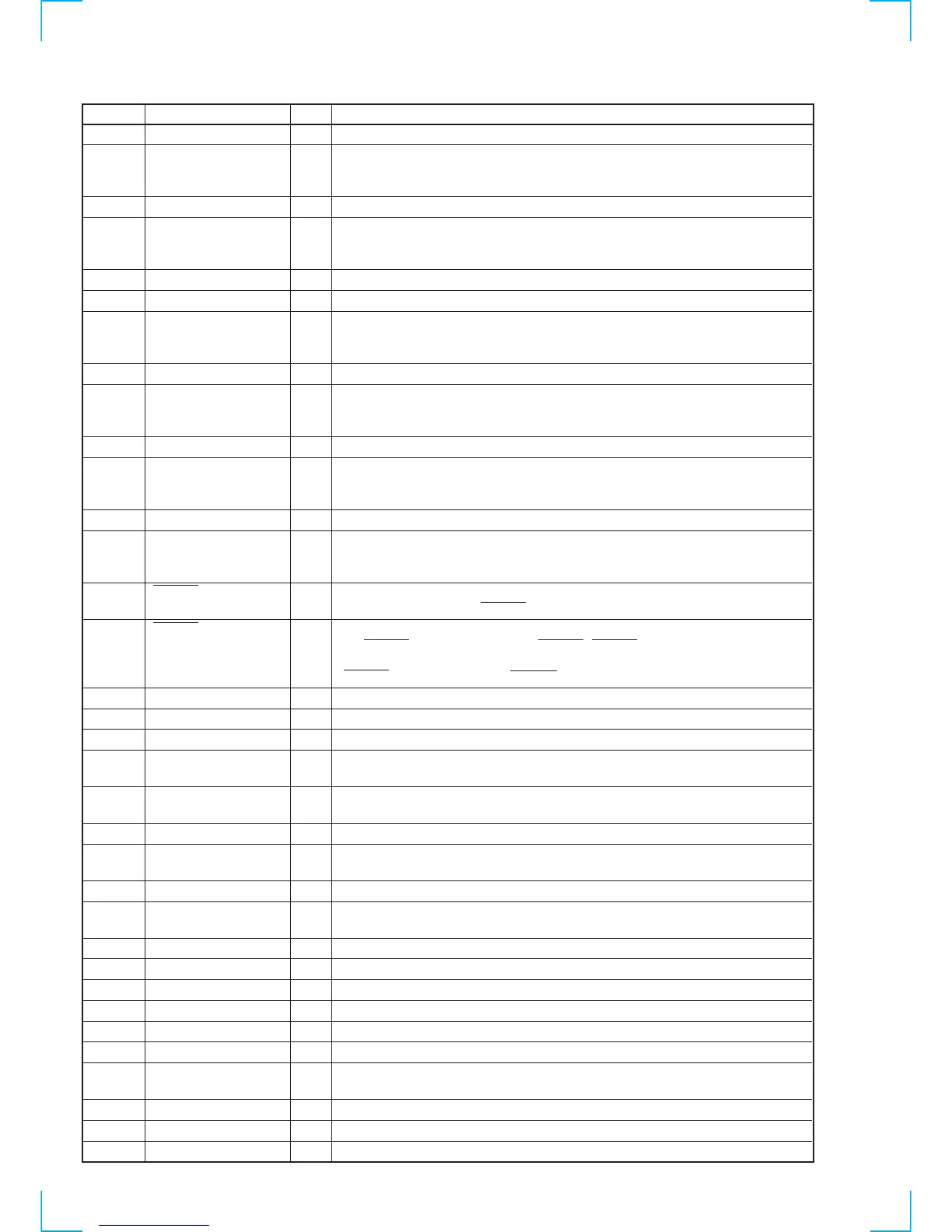

58

141 PIO [10:0] I/O Programmable I/O pins.

142, 143 VDATA [7:0] O Video data bus. Byte serial CdYCrY data synchronous with VCLK. At power-up, the

decoder does not drive VDATA. During boot-up, the decoder uses configuration

parameters to drive or 3-state VDATA.

144 VDD — 3.3-V supply voltage for core logic and I/O signals.

145 VDATA [7:0] O Video data bus. Byte serial CdYCrY data synchronous with VCLK. At power-up, the

decoder does not drive VDATA. During boot-up, the decoder uses configuration

parameters to drive or 3-state VDATA.

146 VSS — Ground for core logic and I/O signals.

147 PIO [10:0] I/O Programmable I/O pins.

148 VDATA [7:0] O Video data bus. Byte serial CdYCrY data synchronous with VCLK. At power-up, the

decoder does not drive VDATA. During boot-up, the decoder uses configuration

parameters to drive or 3-state VDATA.

149 VDD — 3.3-V supply voltage for core logic and I/O signals.

150 VDATA [7:0] O Video data bus. Byte serial CdYCrY data synchronous with VCLK. At power-up, the

decoder does not drive VDATA. During boot-up, the decoder uses configuration

parameters to drive or 3-state VDATA.

151 VSS — Ground for core logic and I/O signals.

152 VDATA [7:0] O Video data bus. Byte serial CdYCrY data synchronous with VCLK. At power-up, the

decoder does not drive VDATA. During boot-up, the decoder uses configuration

parameters to drive or 3-state VDATA.

153 PIO [10:0] I/O Programmable I/O pins.

154, 155 VDATA [7:0] O Video data bus. Byte serial CdYCrY data synchronous with VCLK. At power-up, the

decoder does not drive VDATA. During boot-up, the decoder uses configuration

parameters to drive or 3-state VDATA.

157 HSYNC I/O Horizontal sync. The decoder begins outputting pixel data for a new horizontal line after

the falling (active) edge of HSYNC.

158 VSYNC I/O Vertical sync. Bi-directional, the decoder outputs the top border of a new field on the

first HSYNC after the falling edge of VSYNC. VSYNC can accept vertical

synchronization or top/bottom field notification from an external source.

(VSYNC HIGH=Bottom field. VSYNC LOW=Top field)

160 VDD — 3.3-V supply voltage for core logic and I/O signals.

161 DA-DATA O Serial audio samples relative to DA-BCK clock.

162 VSS — Ground for core logic and I/O signals.

166 DA-LRCK O PCM left-right clock. Identifies the channel for each audio sample. The polarity is

programmable.

167 DA-BCK O PCM bit clock. Divided by 8 from DA-XCX, DA-BCK can be either 48 or 32 times the

sampling clock.

168 VDD — 3.3-V supply voltage for core logic and I/O signals.

169 DA-XCX I/O Audio external frequency clock. Used to generate DA-BCK and DA-LRCK. DA-XCK

can be either 384 or 256 times the sampling frequency.

170 VSS — Ground for core logic and I/O signals.

171 DAI-DATA I PCM input data, two channels. Serial audio samples relative to DA-BCK clock,

resulting in downmixed audio output.

172 DAI-LRCK I PCM input left-right clock.

173 DAI-BCK I PCM input bit clock.

174 PIO [10:0] I/O Programmable I/O pins.

175 VDD — 3.3-V supply voltage for core logic and I/O signals.

176 A-VDD — 3.3-V analog supply voltage.

177 VCLK I Video clock. Clocks out data on input. VDATA [7:0]. Clock is typically 27 MHz.

178 SYSCLK I System clock. Decoder requires an external 27 MHz TTL oscillator. Drive with the

same 27-MHz as VCK.

179 A-VSS — Analog ground for PLL.

180 CD-DATA I Serial CD data.

181 VDD — 3.3-V supply voltage for core logic and I/O signals.

Pin No.

Pin Name

I/O Function

Loading...

Loading...