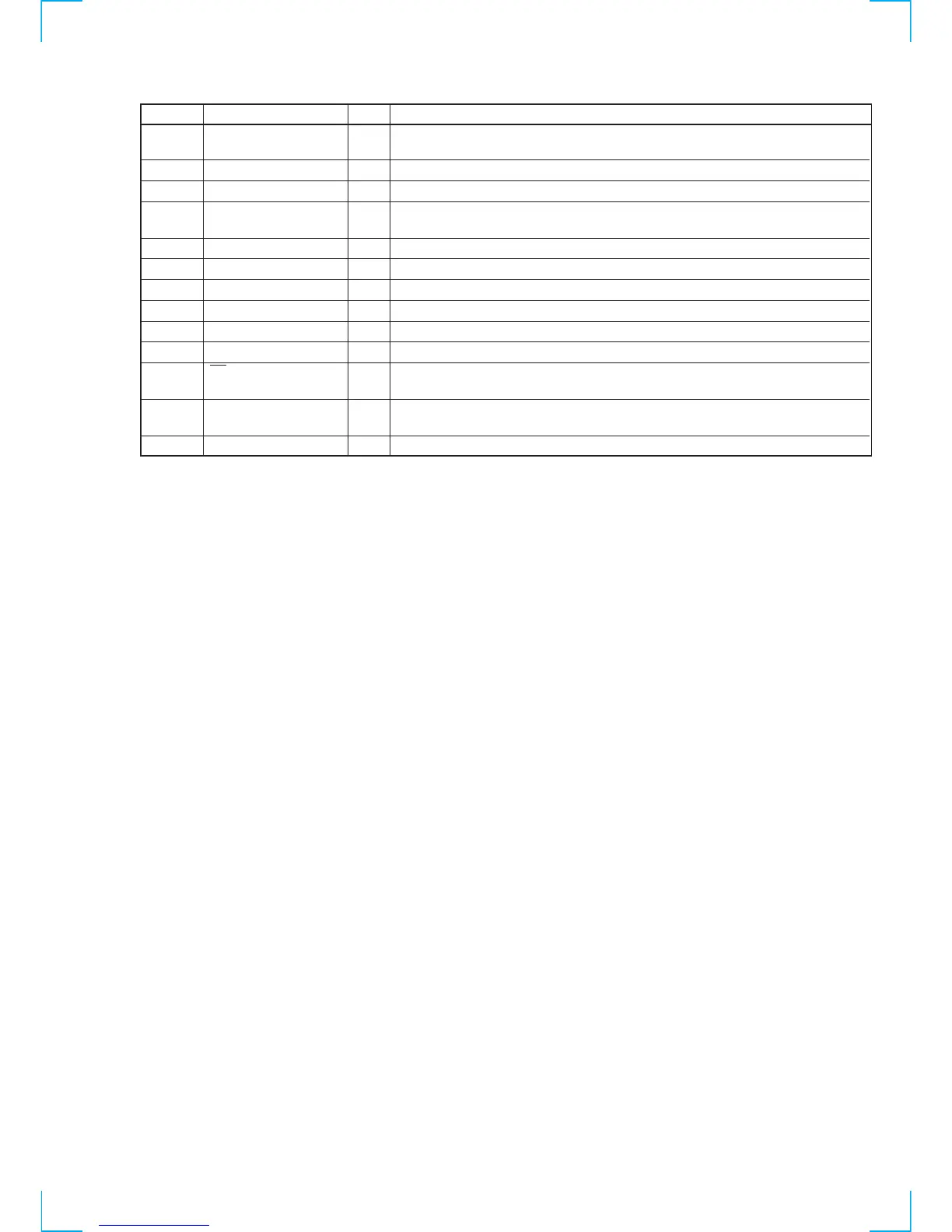

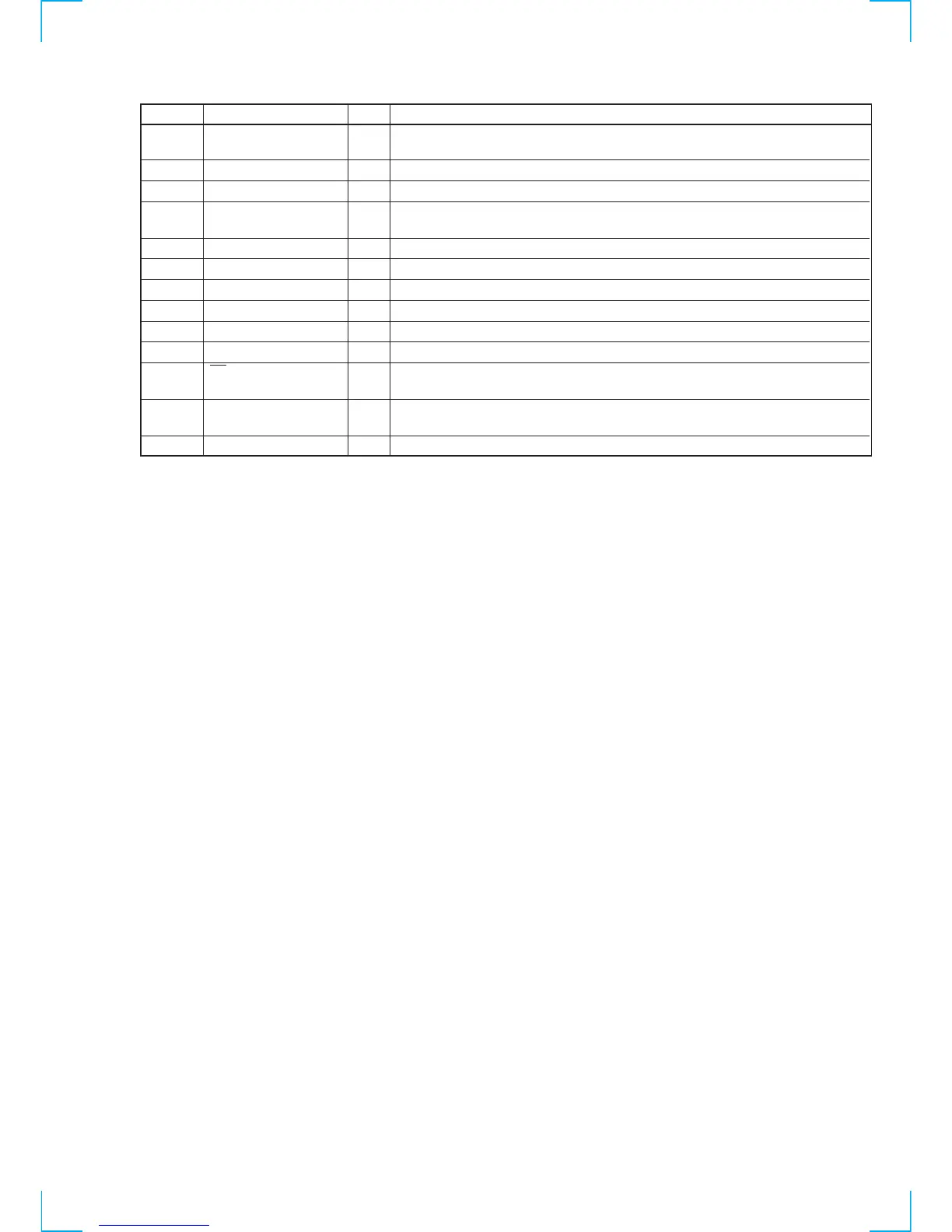

59

182 CD-LRCK I Programmable polarity 16-bit word synchronization to the decoder

(right channel HIGH).

183 VSS — Ground for core logic and I/O signals.

184 CD-BCK I CD bit clock. Decoder accept multiple BCK rates.

185 CD-C2PO I Asserted HIGH indicates a corrupted byte. Decoder keeps the previous valid picture

on-screen until the next valid picture is decoded.

190 PIO [10:0] I/O Programmable I/O pins.

193 VDD — 3.3-V supply voltage for core logic and I/O signals.

195 VSS — Ground for core logic and I/O signals.

197 VDD — 3.3-V supply voltage for core logic and I/O signals.

199 VSS — Ground for core logic and I/O signals.

202 to 204 HADDR [2:0] I Host address bus. 3-bit address bus selects one of eight host interface registers.

206 CS I Host chip select. Host asserts CS to select the decoder for a read or write operation.

The falling edge of this signal triggers the read of write operation.

207 R/W I Read/write strobe in M mode. Write strobe in I mode. Host asserts R/W LOW to select

write and LOW to select Read.

208 RD I Read strobe in I mode. Must be held HIGH in M mode.

Pin No.

Pin Name

I/O Function

Loading...

Loading...