5-6

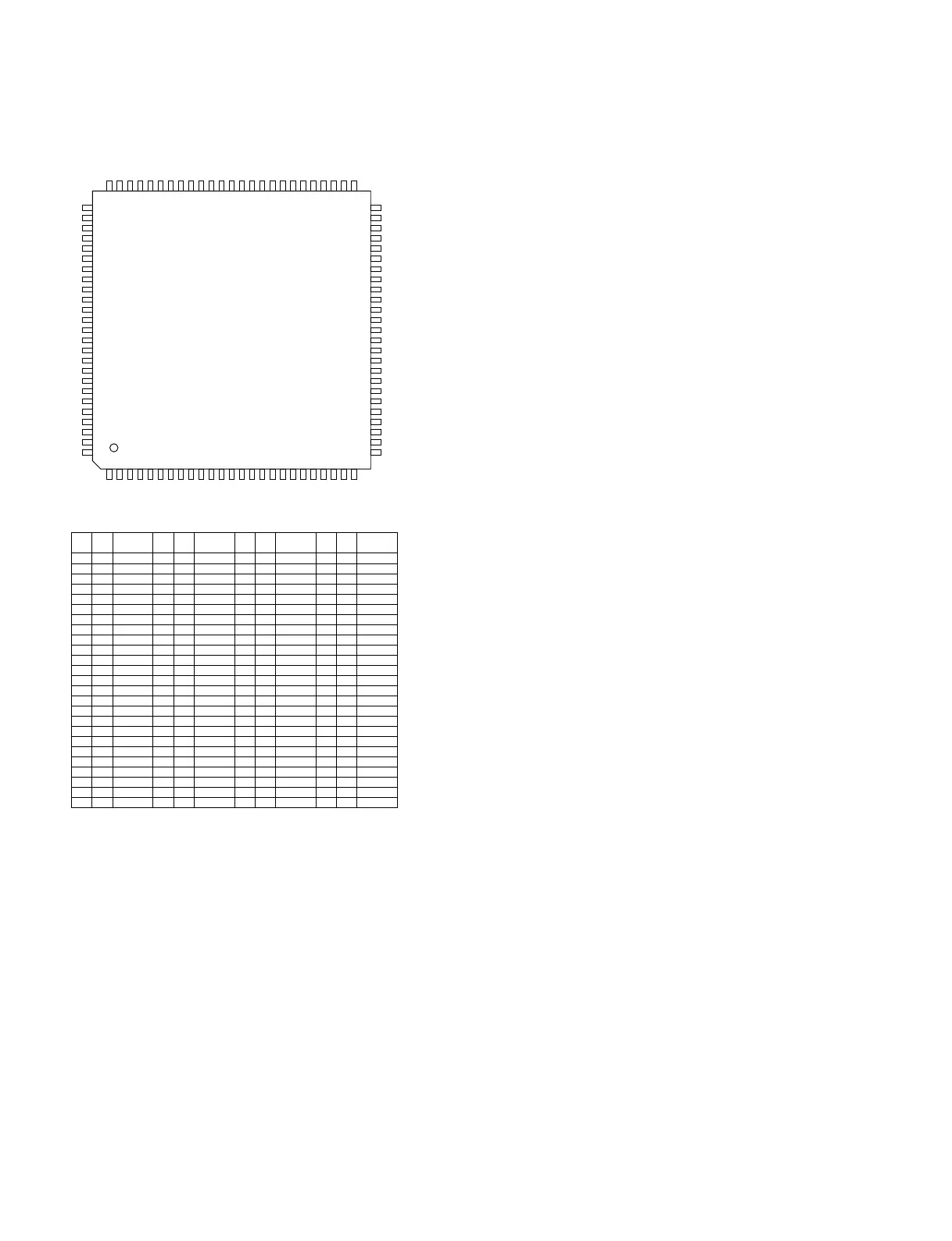

SSC-DC593/DC593P/DC598P (E)

CXD9160TQ (SONY)

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

CAMERA SIGNAL PROCESSOR

—TOP VIEW—

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

—

—

I

I

I

I

I

I

I

—

—

O

O

—

—

I

I

I

O

I

I

O

O

—

—

V

CC

(3.3 V)

V

CC

(2 V)

PBLK

BUNRI

TMC1

TMC2

MODE1

MODE2

TEB

D.V

CC

A.V

CC

YOUT

COUT

A.GND

D.GND

AMC

SMC

XSG1

SYNCO

XV1

TEST0

PLLHVEN

PLLHV

V

CC

(2 V)

V

CC

(3.3 V)

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

—

I

I

O

O

O

I

I

I

I

O

I

I

I

I

I

I

O

O

O

O

I

—

I

—

GND

I4FSC

TEST1

PLLSC

SCGATE

FSCO

FSCI

EXTSCI

EXTSYNCI

EXTVDI

SO

SI

XSCE

XSCK

XCLR

CHARM

CHARB

CGCK

HDO

VDO

VGATE

LID

GND

VCK

GND

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

—

—

O

O

I

I

I

I

I

I

I

I

I

I

O

O

O

O

O

—

I

—

O

—

—

VCC (3.3 V)

VCC (2 V)

TGHD

TGVD

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

CLPOB

ADCK

FLDO

MEMCK

MEMCID

GND

MCK

GND

CO3

V

CC

(2 V)

V

CC

(3.3 V)

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

—

O

O

O

I

I

I

I

O

O

O

O

O

O

O

O

I

I

I

I

I

I

I

I

—

GND

CO2

CO1

CO0

CI3

CI2

CI1

CI0

YO7

YO6

YO5

YO4

YO3

YO2

YO1

YO0

YI7

YI6

YI5

YI4

YI3

YI2

YI1

YI0

GND

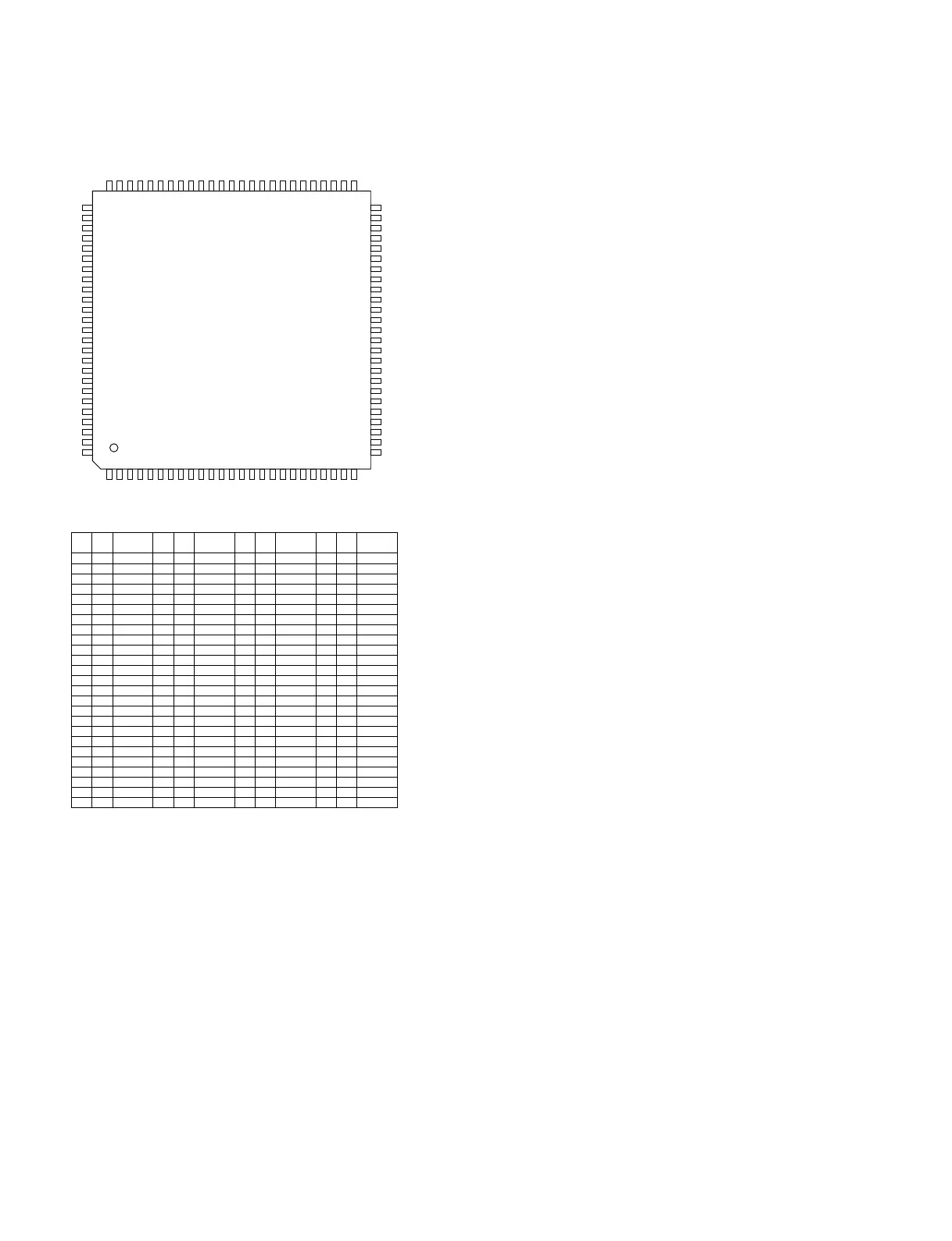

PIN

NO.

I/O SIGNAL

PIN

NO.

I/O SIGNAL

PIN

NO.

I/O SIGNAL

PIN

NO.

I/O SIGNAL

INPUTS

AMC

BUNRI

CHARB

CHARM

CI0 - CI3

D0 - D9

EXTSCI

EXTSYNCI

EXTVDI

FSCI

I4FSC

LID

MCK

MODE1, MODE2

PBLK

SI

SMC

TEB

TEST1, TEST0

TMC1, TMC2

VCK/SCK

XCLR

XSCE

XSCK

XSG1/SIN

XV1

YI0 - YI7

OUTPUTS

ADCK

CGCK

CLPOB

CO0 - CO3

COUT

FLDO

FSCO

HDO

MEMCID

MEMCK

PLLHVEN

PLLHV

PLLSC

SCGATE

SO

SYNCO/SOUT

TGHD

TGVD

VDO

VGATE

YO0 - YO7

YOUT

: ATG MODE CONTROL

: DAC TEST MODE SELECT (FIXED:L)

: CHARACTER CONTROL (BACK GROUND)

: CHARACTER CONTROL (CHARACTER)

: CHROMA SIGNAL MEMORY INTERFACE

: DIGITAL SIGNAL DATA FROM A/D

: EXT BURST

: EXT SYNC SIGNAL (COMPOSITE SYNC/HORIZONTAL SYNC)

: EXT SYNC SIGNAL (VERTICAL SYNC)

: PLLSC INNER SUB CARRIER

: 4FSC (FOR SUB CARRIER GENERATOR)

: LINE DISCRIMINATION SIGNAL

: MASTER CLOCK

: DAC TEST MODE SELECT (FIXED: L)

: PREBLANKING PULSE

: SERIAL DATA FOR CPU INTERFACE

: SCAN MODE SELECT

: MEMORY TEST ENABLE (NORMAL:H)

: TEST MODE SET (50k PULL DOWN)

: TEST MODE SET (FIXED: L)

: SG CLOCK (NTSC: 14.318MHz, PAL: 14.1875MHz) /SCAN CLOCK

: SYSTEM RESET

: CHIP SELECT FOR CPU INTERFACE

: SERIAL CLOCK FOR CPU INTERFACE

: CCD SENSOR ELECTRIC CHARGE READ PULSE/SCAN IN

: CCD VERTICAL REGISTER CLOCK

: LUMINANCE SIGNAL MEMORY INTERFACE

: CLOCK FOR A/D CONVERTER

: CLOCK FOR ON SCREEN DISPLAY IC

: OPB BLOCK CLAMP PULSE

: CHROMA SIGNAL MEMORY INTERFACE

: CHROMA SIGNAL

: FIELD DISCRIMINATION

: SUB CARRIER

: HORIZONTAL SYNC

: COLOR DISCRIMINATION FOR MEMORY INTERFACE

: CLOCK FOR MEMORY INTERFACE

: H-PLL/V-PLL PHASE COMPARATOR ENABLE

: H-PLL/V-PLL PHASE COMPARATOR

: PHASE COMPARATOR OUTPUT FOR SUB CARRIER

: SUB CARRIER GATE PULSE

: SERIAL DATA FOR CPU INTERFACE

: COMPOSITE SYNC/SCAN OUT

: HORIZONTAL SYNC SIGNAL OUTPUT FOR TG

: VERTICAL SYNC SIGNAL OUTPUT FOR TG

: VERTICAL SYNC

: ELECTRICAL ZOOM CONTROL FOR TG

: LUMINANCE SIGNAL MEMORY INTERFACE

: LUMINANCE SIGNAL

IC

Loading...

Loading...