AN2752 Reset control

Doc ID 14651 Rev 3 15/42

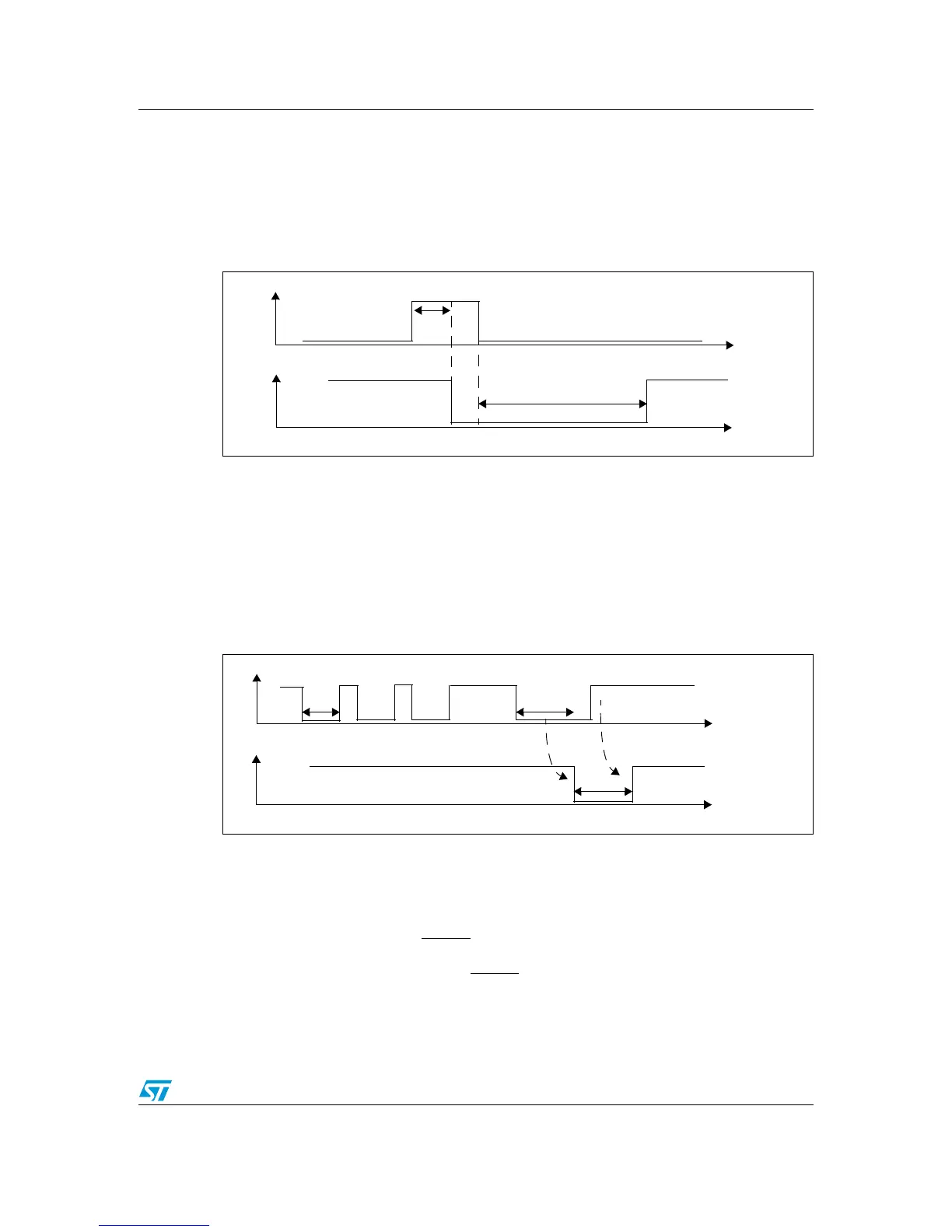

Output characteristics

● A valid pulse on the pin is guaranteed with a ≥ 20 ns pulse duration on the internal

output buffer.

● After a valid pulse is recognized, a pulse on the pin of at least 20 µs is guaranteed

starting from the falling edge of A.

Figure 8. Output characteristics

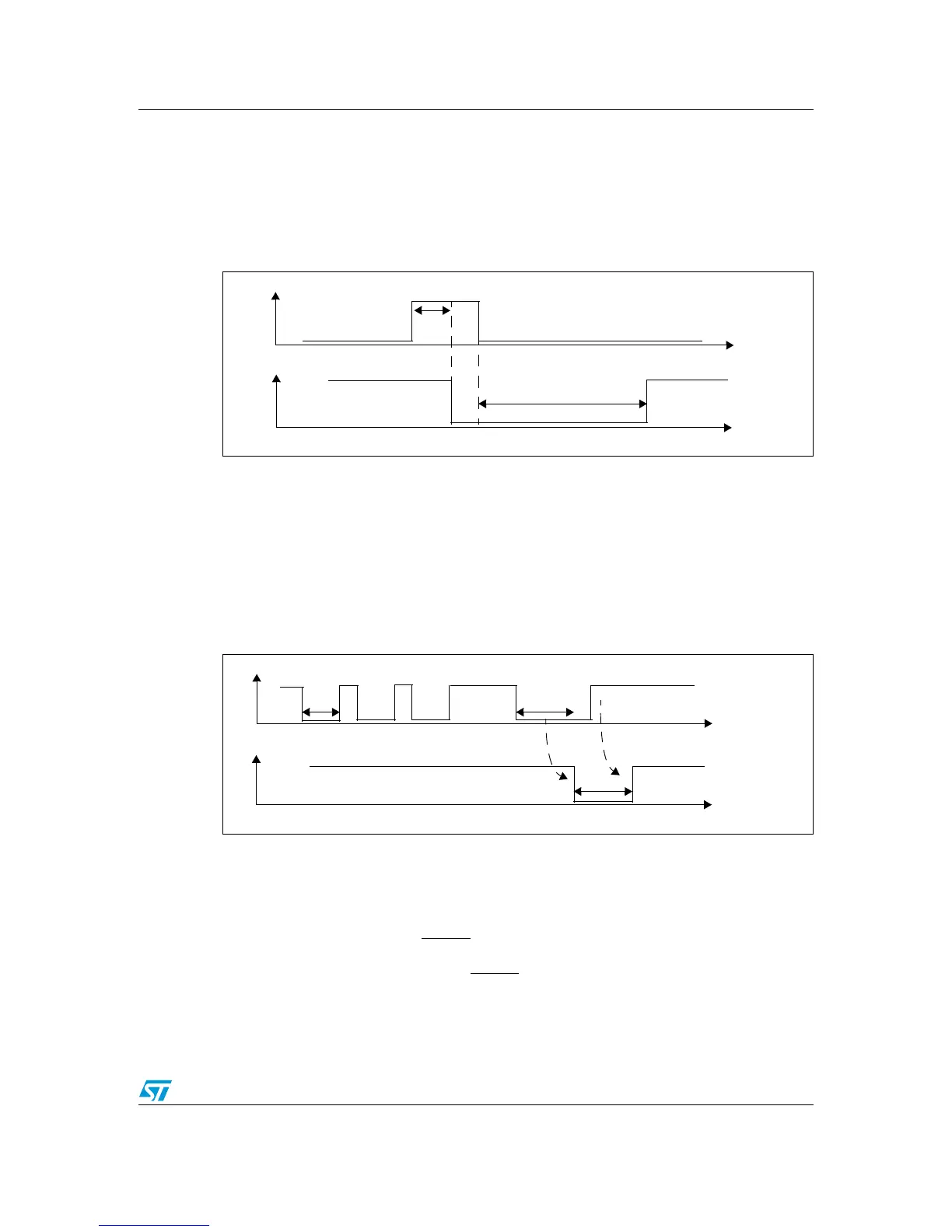

Input characteristics

● All pulses with a duration less than 75 ns are filtered

● All train/burst spikes with a ratio of 1/10 must be filtered. This means that a negative

spike of up to 75 ns is always filtered, when a 7.5 ns interval between spikes occurs

(ratio 1/10).

● All pulses with duration more than 450 ns are recognized as valid pulses

● After a valid pulse is recognized, an internal pulse of at least 30 ns is guaranteed

Figure 9. Input characteristics

5.2 Hardware reset implantation

There are several reset implementation schemes to choose from, such as power supply

behavior, based on the specific parameters of the application. Whatever the solution

chosen, the idea is to keep the RESET

pin at a low logic level until the supply has reached a

safe operating voltage. Therefore, the external circuit should be designed in such a manner

that there is enough delay to keep the RESET

pin below the V

IL

value.

Loading...

Loading...