AN2752 Reference design

Doc ID 14651 Rev 3 21/42

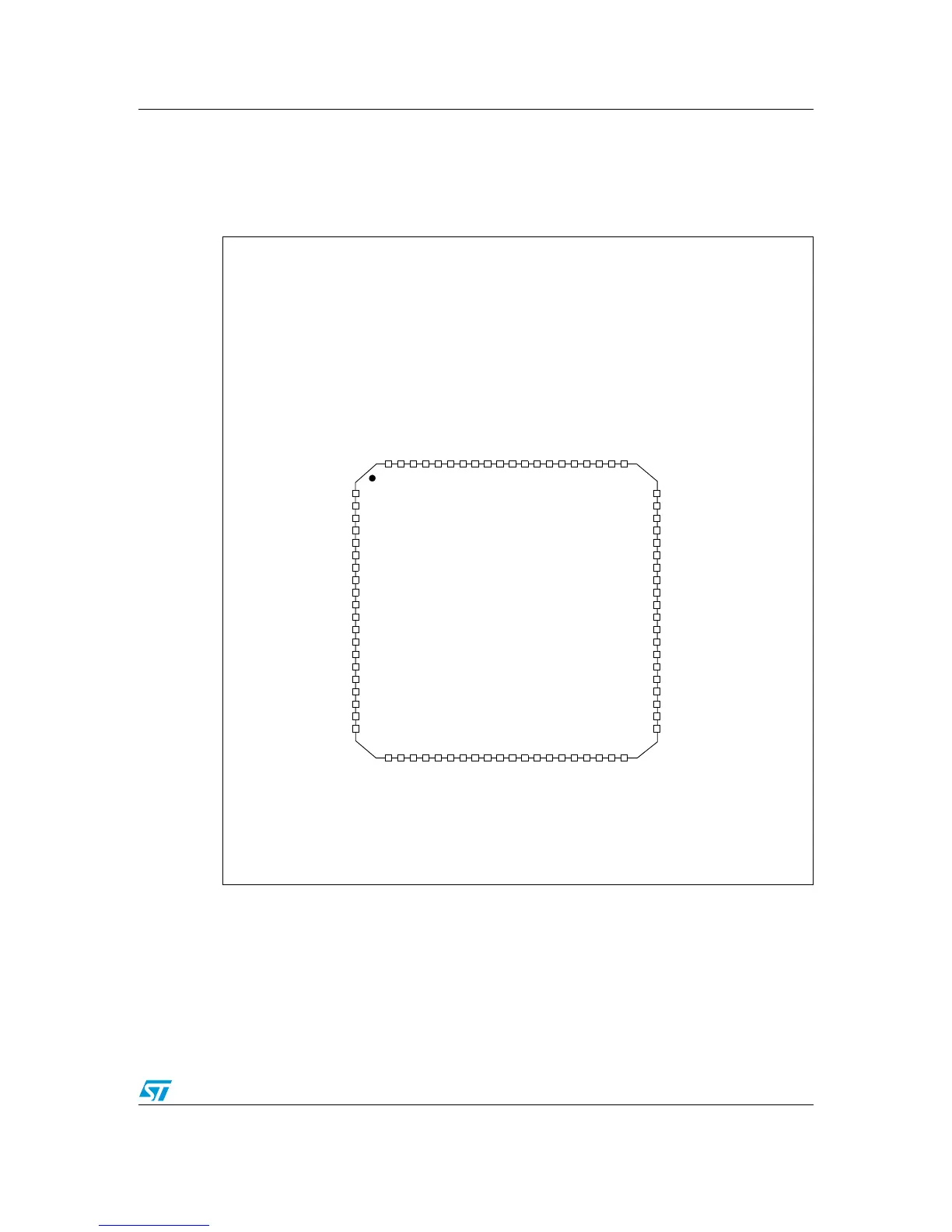

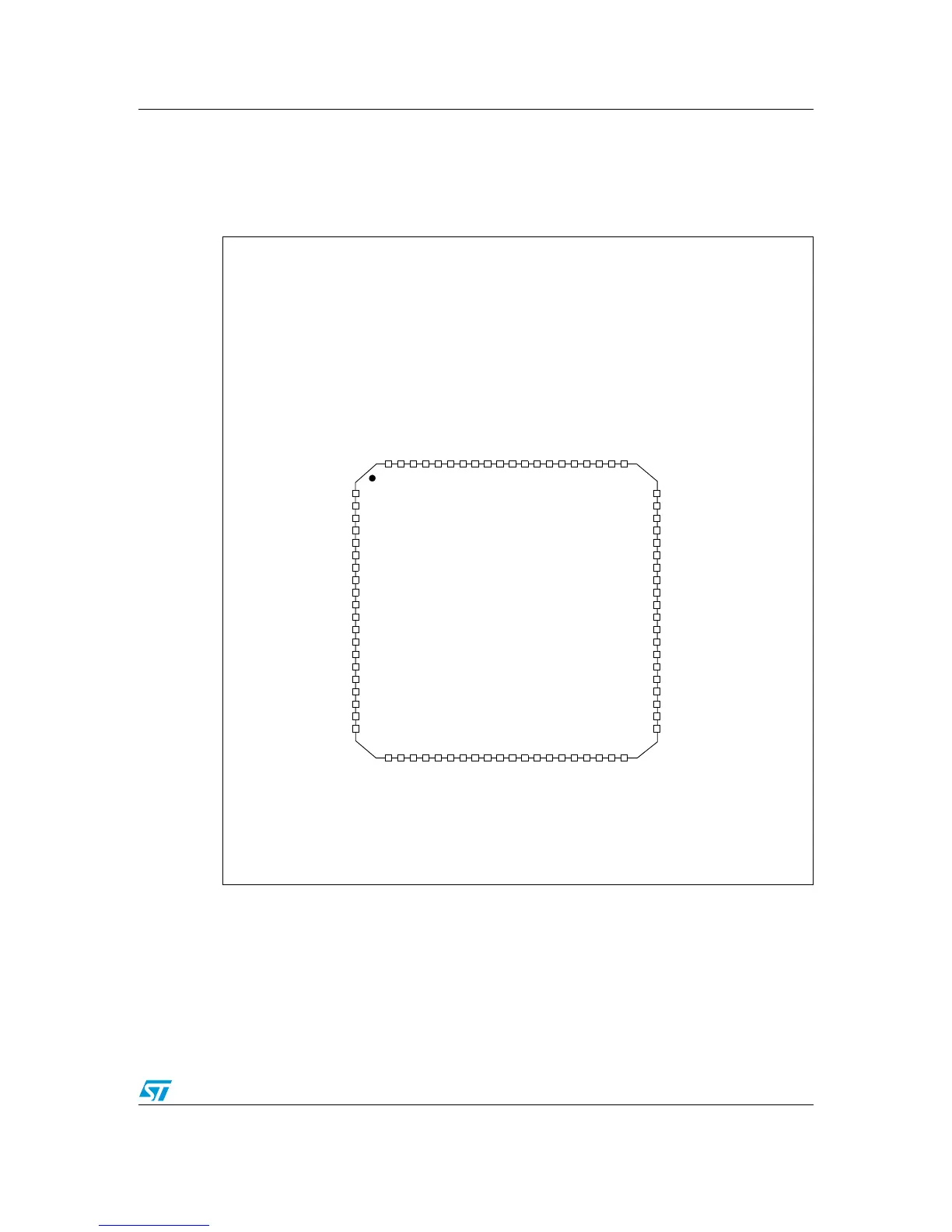

7.3 Pinouts

STM8S devices have several package types, including the LQFP 80-pin pinout shown in

Figure 12. Please refer to the Root part number 2 datasheet for more details.

Figure 12. LQFP 80-pin pinout

1. (HS) high sink capability.

2. [ ] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a

duplication of the function).

PD4 (HS)/TIM2_CH1[BEEP]

2

1

3

4

5

6

7

8

10

9

12

14

16

18

20

11

15

13

17

19

25

26

28

27

30

32

34

36

38

29

33

31

35

37

39

57

58

56

55

54

53

52

51

49

50

47

45

43

41

48

44

46

42

60

59

61

62

63

64

66

68

65

67

69

70

71

72

74

73

75

76

77

78

79

80

PI4

PI3

PI2

PI1

PC4 (HS)/TIM1_CH4

PC3 (HS)/TIM1_CH3

PC2 (HS)/TIM1_CH2

PC1 (HS)/TIM1_CH1

PG6

PG5

PI5

PI0

PG4

PG3

PG2

PC7/SPI_MISO

V

SSIO_2

V

DDIO_1

[TIM3_CH1]TIM2_CH3/PA3

UART1_RX/PA4

UART1_TX/PA5

AIN12/PF4

V

SSIO_1

V

SS

VCAP

V

DD

UART1_CK/PA6

(HS) PH0

(HS) PH1

PH2

PH3

AIN15/PF7

AIN14/PF6

AIN13/PF5

NRST

OSCIN/PA1

OSCOUT/PA2

[I2C_SDA]AIN5/PB5

[I2C_SCL]AIN4/PB4

[TIM1_CH2N]AIN1/PB1

[TIM1_CH1N]AIN0/PB0

AIN8/PE7

V

REF-

AIN10/PF0

AIN7/PB7

AIN6/PB6

TIM1_ETR/PH4

TIM1_CH3N/PH5

TIM1_CH2N/PH6

40

AIN9/PE6

21

22

24

23

AIN11/PF3

V

REF+

V

DDA

V

SSA

PD0(HS)/TIM3_CH2[TIM1_BKIN][CLK_CCO]

PE2/I

2

C_SDA

PE3/TIM1_BKIN

PE4

PG7

PD7/TLI[TIM1_CH1]

PD6/UART3_RX

PD5/UART3_TX

PI7

PI6

PD2 (HS)/TIM3_CH1[TIM2_CH3]

PD1 (HS)/SWIM

PC5/SPI_SCK

PC6/SPI_MOSI

PG0/CAN_TX

PG1/CAN_RX

PE0/CLK_CCO

PD3 (HS)/TIM2_CH2[ADC_ETR]

[TIM1_ETR]/AIN3/PB3

[TIM1_CH3N]AIN2/PB2

PC0/ADC_ETR

PE5/SPI_NSS

TIM1_CH1N/PH7

V

DDIO_2

PE1/I

2

C_SCL

(HS) High sink capability

Loading...

Loading...