Reset control AN2752

14/42 Doc ID 14651 Rev 3

5 Reset control

5.1 Reset management overview

The reset cell is a dedicated 5 V bidirectional I/O. Its output buffer driving capability is fixed

to Iol

MIN

= 2 mA @ 0.4 V in the 3 V to 5.5 V range which includes a 40 k pull-up. Output

buffer is reduced to the n-channel MOSFET (NMOS). If a 40 k pull-up is accepted, this cell

does not include an output buffer of 5 V capability. The receiver includes a glitch filter,

whereas the output buffer includes a 20 µs delay.

There are many reset sources, including:

● External reset through the NRST pin

● Power-on reset (POR) and brown-out reset (BOR): During power-on, the POR keeps

the device under reset until the supply voltage (V

DD

and V

DDIO

) reach the voltage level

at which the BOR starts to function.

● Independent watchdog reset (IWDG)

● Window watchdog reset (WWDG)

● Software reset: The application software can trigger reset

● SWIM reset: An external device connected to the SWIM interface can request the

SWIM block to generate a microcontroller reset

● Illegal opcode reset: If a code to be executed does not correspond to any opcode or

prebyte value, a reset is generated

● Electromagnetic susceptibility (EMS) reset: Generated if critical registers are corrupted

or badly loaded

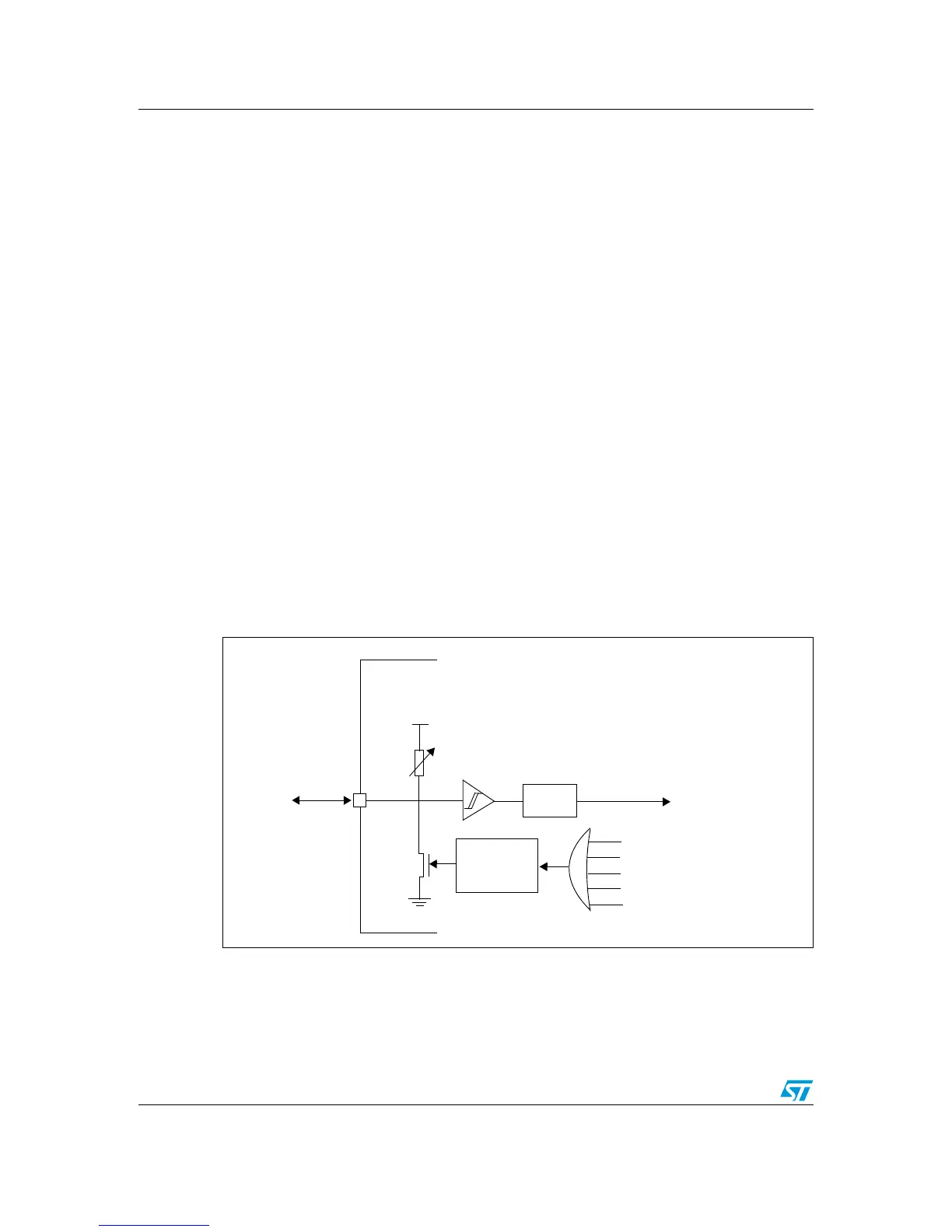

Figure 7. Reset management

Loading...

Loading...