Chapter 2: Installation

2-25

JBR1

JTBT1

JPW3

+

MH12

JSTBY1

JF1

JTPM1

S1

JAUDIO1

JPCIE1

JPCIE2

JD1

JUSBLAN1

JBT1

FAN4

FAN1

FAN2

FAN3

FAN5

S4

S8

S11

7

JUSB30_I4

19

JPW1

1

LED1

LED2

A

C

JPW2

JHD_AC1

JI2C2

JI2C1

JL1

JSPDIF_OUT

JSMB1

JLED1

JSMB2

JPUSB2

1

JPL1

JPME2

JWD1

1

3

DESIGNED IN USA

C7Z170-M

REV:1.00

MAC CODE

BAR CODE

TP104

TP103

TP100

MH2

MH1

Power Button

BIOS Restore

CLEAR CMOS

JHD_AC1:Audio AC97 and HD audio jumper

3 PIN POWER LED

JLED1:

2-3:BIOS RECOVERY

1-2:NORMAL

JBR1:

USB 10/11(3.0)

USB 8/9(3.1)

USB 2/3

USB 4/5(3.0)

USB 6/7(3.0)

HDMI/DP

DVI

1-2 ENABLE

2-3 DISABLE

JPUSB2:USB 8/9 WAKE UP

1-2 ENABLE

2-3 DISABLE

JPUSB1:USB0/1 WAKE UP

PCH SLOT1 PCI-E 3.0 X1

JPAC1

5V STBY POWER

PCH SLOT2 PCI-E 3.0 X4

LAN

KB/MOUSE

JWD1:

JSD1:

LAN

DISABLE

ENABLE

2-3

1-2

JPL1

2-3:NMI

1-2:RST

WATCH DOG

CPU

2-3:ME MANUFACTURING MODE

/CPU FAN

USB 0/1

1-2:NORMAL

JPME2:

SATA DOM PWR

JTPM1:TPM/PORT80

JL1:

AUDIO FP

HDD PWR

LEDLED

CMOS CLEAR

DIMMB1

DIMMB2

NIC1

SPEAKER:1-4

JD1:

BUZZER:3-4

JI2C1/JI2C2

ON:ENABLE

OFF:DISABLE

NIC2

HD AUDIO

OH/FF

LED

CHASSIS INTRUSION

DIMMA1

DIMMA2

RST

PWR

JF1

ON

ALWAYS POPULATE RED SOCKET FIRST

UNB NON-ECC DDR4 DIMM REQUIRED

CPU SLOT3 PCI-E 3.0 X16

M.2 PCI-E X4

COM1

2-3:DISABLE

1-2:ENABLE

JPAC1:AUDIO

I-SATA2

I-SATA3

I-SATA1

I-SATA5

I-SATA0

I-SATA4

BT1

S/PDIF OUT

A. PWR LED

B. COM1

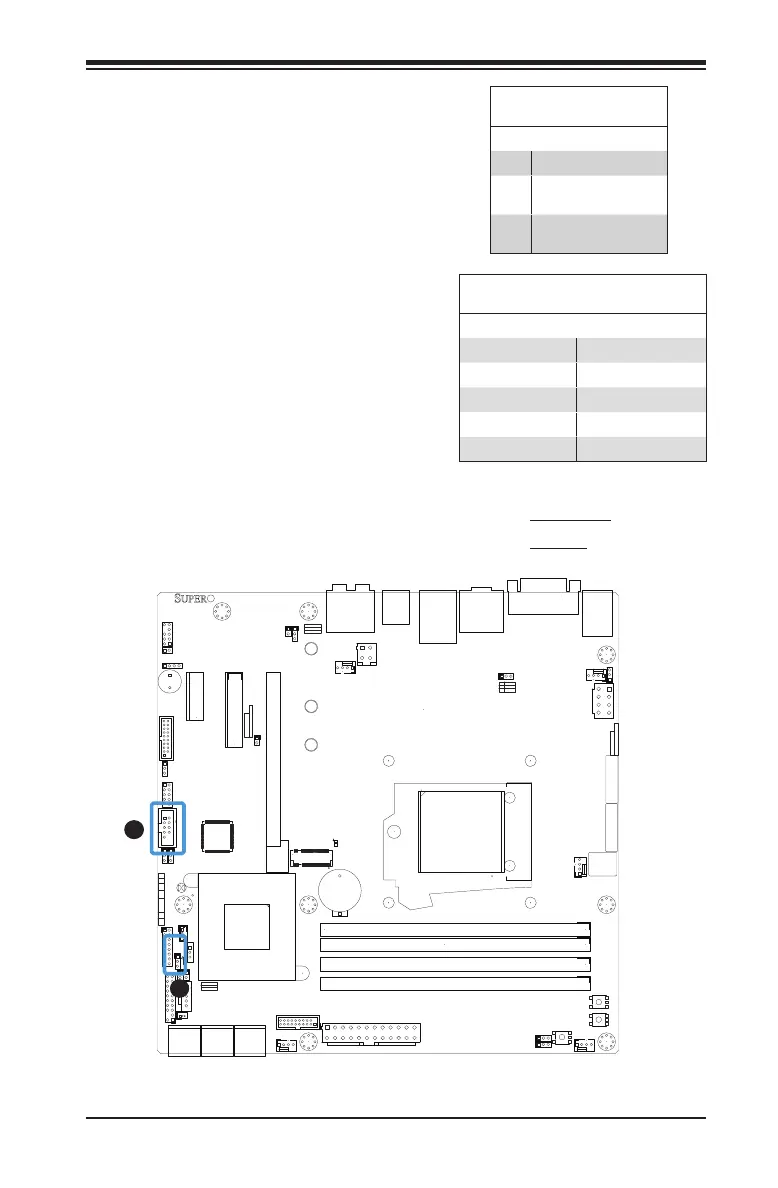

Onboard Power LED (JLED1)

An onboard Power LED header is located

at JLED1. This Power LED header is con-

nected to Front Control Panel located

at JF1 to indicate the status of system

power. See the table on the right for pin

denitions.

Onboard PWR LED

Pin Denitions

Pin# Denition

1 VCC

2 Connection to PWR

LED in JF1

3 Connection to PWR

LED in JF1

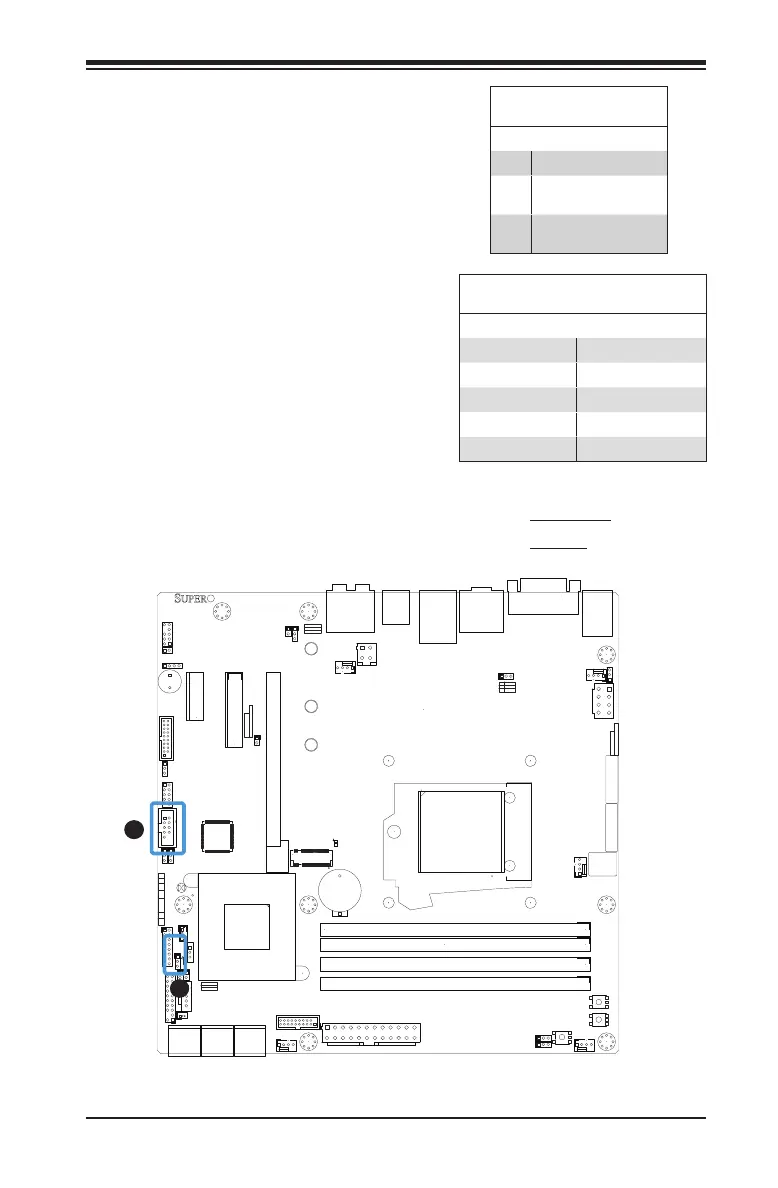

Serial Port (COM1)

There is one serial (COM) port header on

the motherboard. COM1is located next to

the USB 2/3 header. See the table on the

right for pin denitions.

Serial/COM Ports

Pin Denitions

Pin # Denition Pin # Denition

1 DCD 6 DSR

2 RXD 7 RTS

3 TXD 8 CTS

4 DTR 9 RI

5 Ground 10 N/A

A

B

Loading...

Loading...