11.8.5. Read the Status Byte Register

The Status Byte register is a summary of all events that have been enabled. Figure 7 shows the commands

that are used to enable events. The Status Byte is a condition register, that is, reading it will not clear the

contents. To clear the Status Byte register, the connected event registers must be read or cleared.

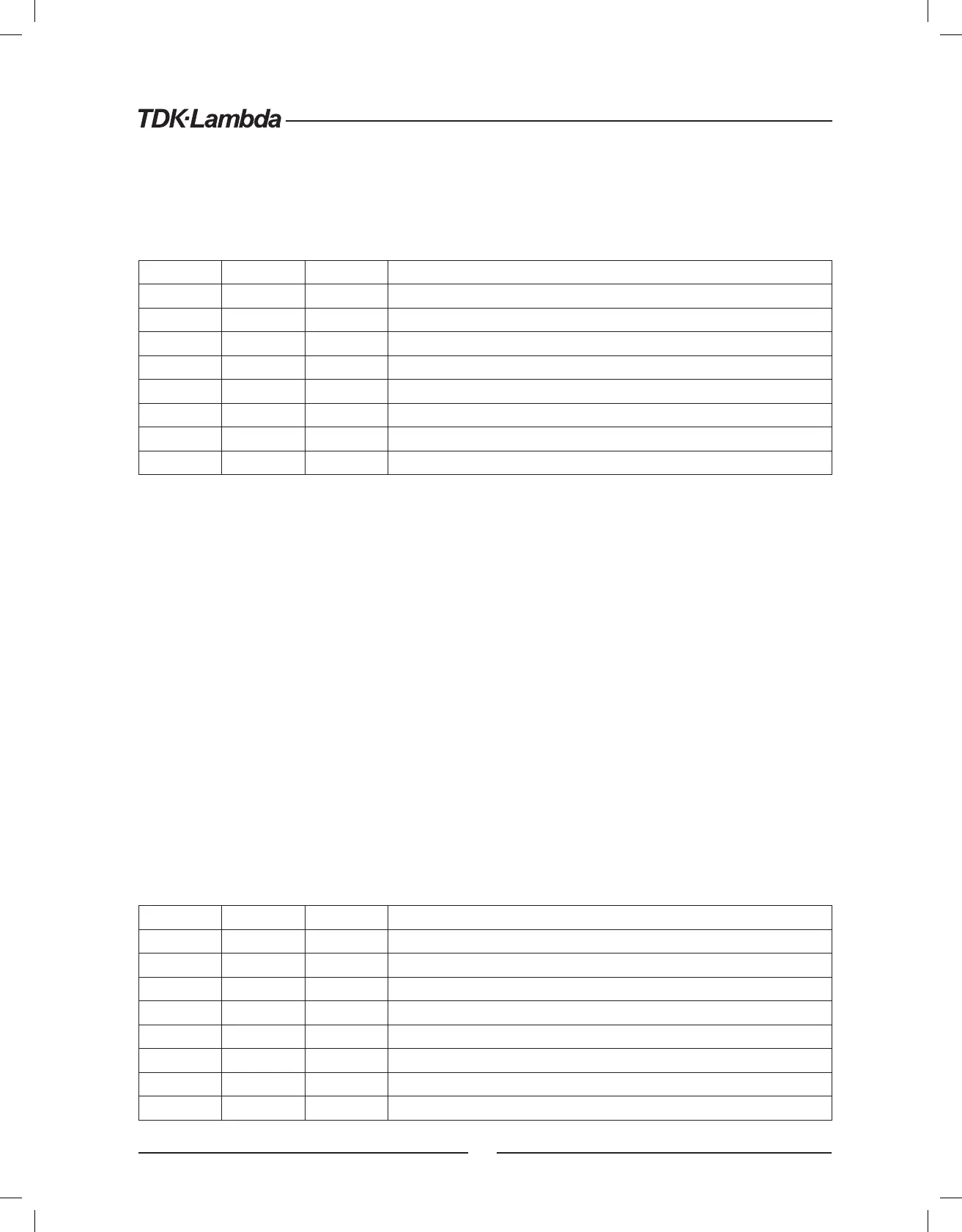

These are the bit assignments of the Status Byte:

BIT VALUE SYMBOL DESCRIPTION

0 1 0 Not Used

1 2 0 Not Used

2 4 SYS System Error, at least one error in error queue

3 8 QUE Questionable Summary

4 16 0 Not Used

5 32 ESB Standard Event Summary

6 64 MSS Master Summary Status, is set if any other bit is set in this register

7 128 OPR Operational Summary

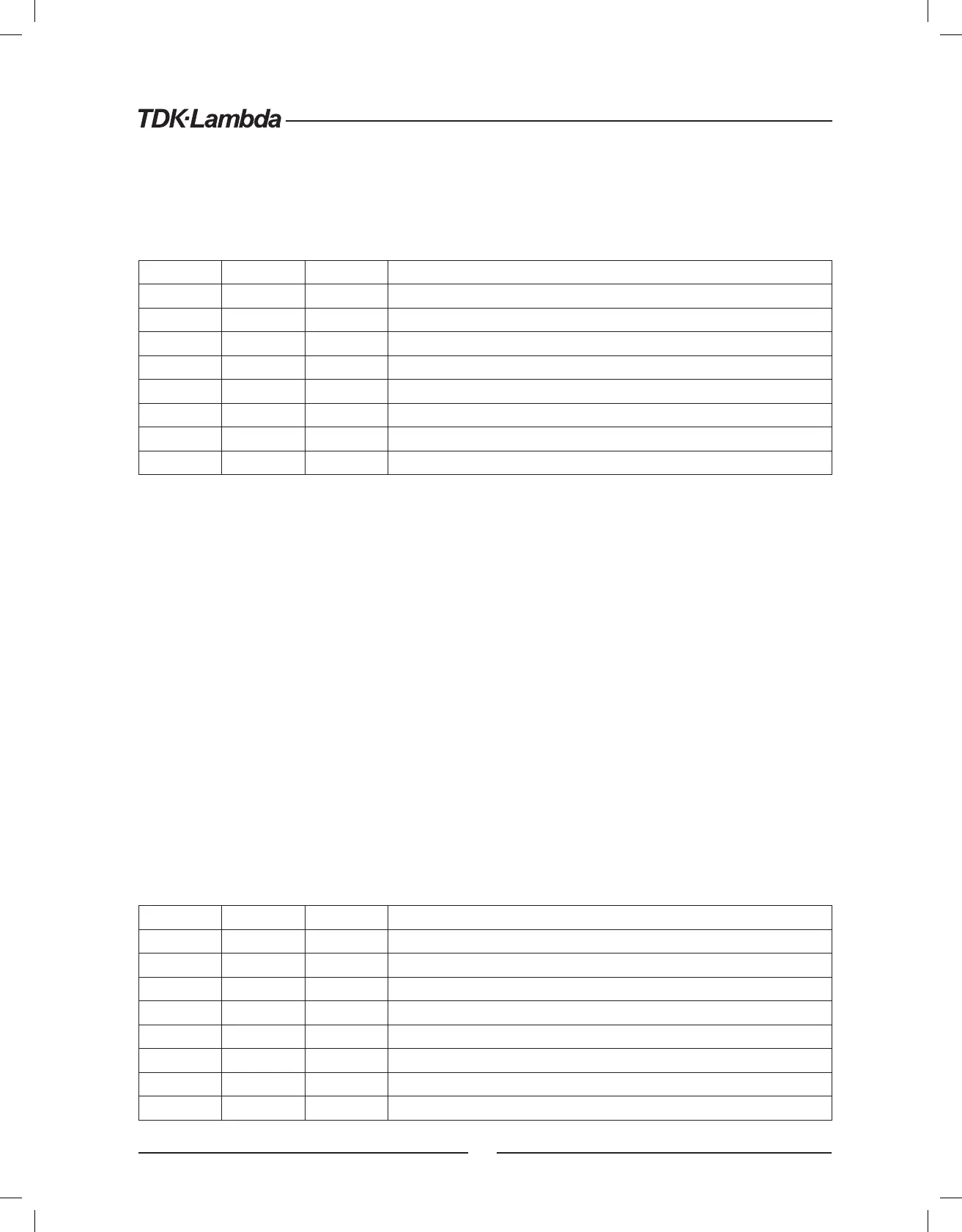

BIT VALUE SYMBOL DESCRIPTION

0 1 OPC Operation complete. See section 11.8.9

1 2 0 Not used

2 4 QYE Query error (response not read)

3 8 DDE Device dependant error (fault shut-down)

4 16 EXE Execution error (could not execute command)

5 32 CME Command error (invalid command received)

6 64 0 Not used

7 128 PON Power On. Set once when power is switched on.

Syntax:

*STB ?

Response: <nnn>, a number from 0 to 255

Example:

12 (a supply fault had occurred and there is some error which may be read

using the SYSTEM:ERROR? query)

11.8.6. Set the Service Request Enable Register

The IEEE-488.2 and SCPI specifications defined this register so instruments may generate a service request

when selected events occur.

The Genesys™ power supply LAN option does not support the service request feature, although the *SRE

command will set bit 6 in the Status Byte.

Syntax:

*SRE <nnn>

Parameter: <nnn> is a number from 0 to 255. The bit assignments are the same as the

Status Byte, in the table above

Example:

*SRE 255 will cause Status Byte bit 6 to be set if any other bit is set

Query:

*SRE? will return 172 in the example

(bits 0,1,4 and 6 are not settable in the *SRE register)

11.8.7. Read the Standard Event Status Event Register

This is a basic status and fault register that was first defined in IEEE-488.2. It is an event register, which

means bits are set to “1” when a condition occurs and they are not cleared until the register value is read

using the

*ESR? query or the *CLS command

These are the bit assignments of the ESR register:

49

Loading...

Loading...