58

7.8.2 Conditional registers

7.8.3 Service Request: Enable and Event Registers

The conditional Registers arecontinuously monitored. Whenachange is detectedina

registerbit which is enabled, the power supplywill generate an SRQ message.

The SRQ message is: "!nn" terminated by CR, wherethe nn is thepower supply address.

The SRQ will be generatedeither in Local or Remote mode.

Output is ON and the supplyis not in

CV.

Output is On and the

supplyinCV.

Output is ON and the supplyis not in

CC.

Output is ON and the

supplyin CC.

The power supply is

operating normally or

fault reporting is not

enabled.

See “OUT n”

command in Section

7.7.5.

One or morefaults are active and

faultreportingis enabled (using

“FENA xx”).

1

2

Constant

Voltage

Constant

Current

No Fault

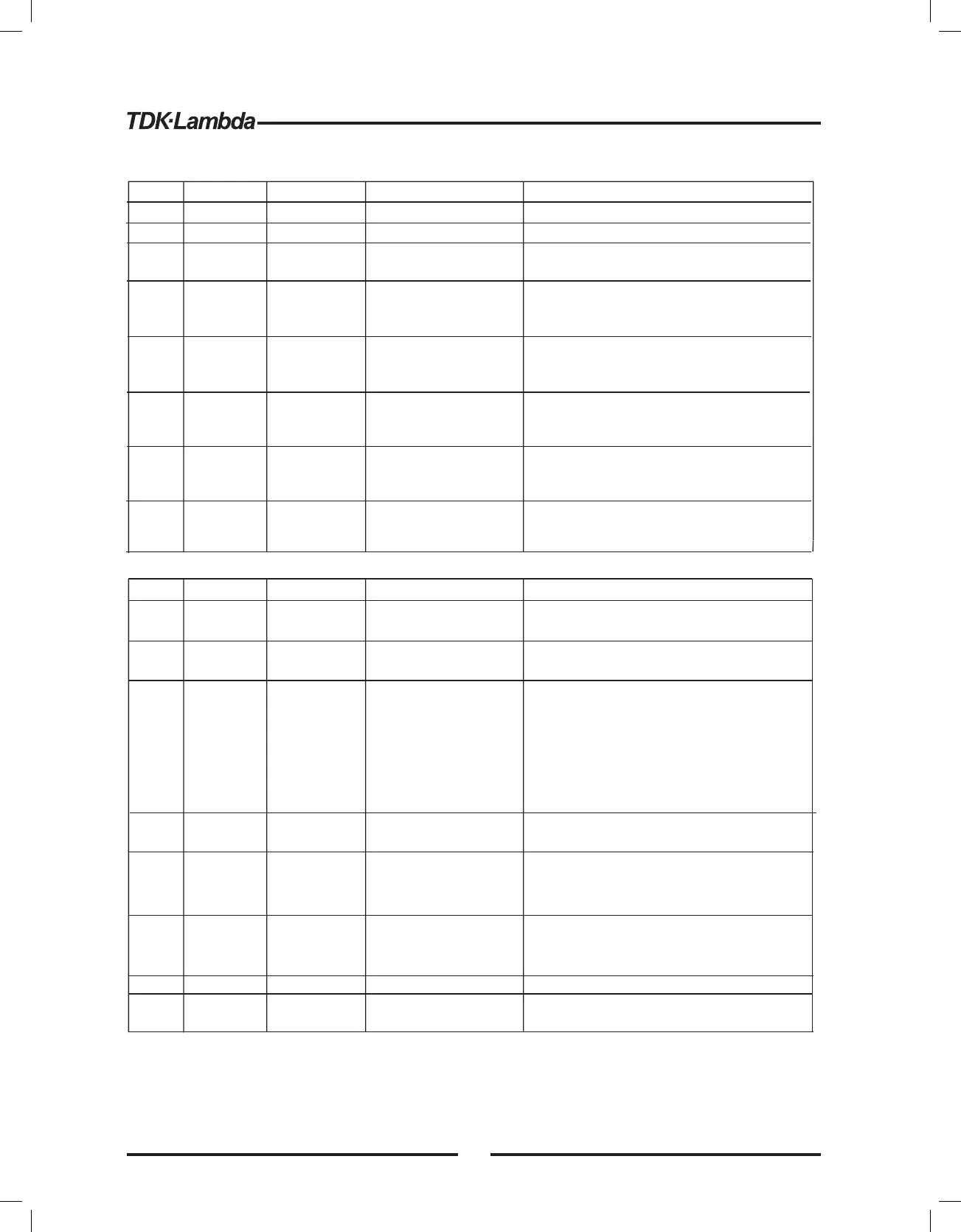

Table7-8: Fault Condition Register

BIT

Fault name

Fault symbol

Bit Set condition

Bit Reset condition

Fixed to zero

Fixed to zeroSPARESparebit

0 (LSB)

The AC input returnsto normal.

AC fail has occurred.

OTP shutdown has

occurred.

The power supply cools down.

Foldback shutdown

has occurred.

The supply output is turned On by

front panel buttonor OUT 1

command.

The supply output is turned On by

front panel buttonor OUT 1

command.

The supply output is turned On by

front panel buttonor OUT 1

command.

OVP shutdown has

occurred.

Rear panelJ"Shut

Off" condition has

occurred.

Rear panel J1 "Shut Off" condition

removed.

Front panel OUT

button pressed to Off.

Rear panel J1 Enable

terminals(J1-1&J1-14)

opened.

Rear panel J1 Enableterminalsclosed.

1

2

3

4

5

6

7(MSB)

AC Fail

Over

temperature

Foldback

Over

voltage

Shut Off

Output Off

Enable

AC

OTP

FOLD

OVP

SO

OFF

ENA

Table7-9:Status Condition Register

BIT

Status name

Status symbol

Bit Set condition

Bit Reset condition

0 (LSB)

CV

CC

NFLT

One or more faults are

enabled and occur.

Fault Event Register cleared (FEVE?).

Supplyisin Auto-

Restart mode (from

Front Panel or serial

command).

Supplyisin Safe-Startmode (from

Front Panelorserialcommand).

Foldprotection

enabled (fromFront

Panel or serial

command).

Foldprotectiondisabled (fromFront

Panel or serial command).

Fixed to zero.

Fixed to zero.

Supplyin Local mode.

Supplyin Remote mode or Local-

Lockout mode.

3

4

5

6

7 (MSB)

Fault

active

Fold

Enabled

Sparebit

Local Mode

FLT

FDE

SPARE

LCL

AST

Auto-

Restart

Enabled

59

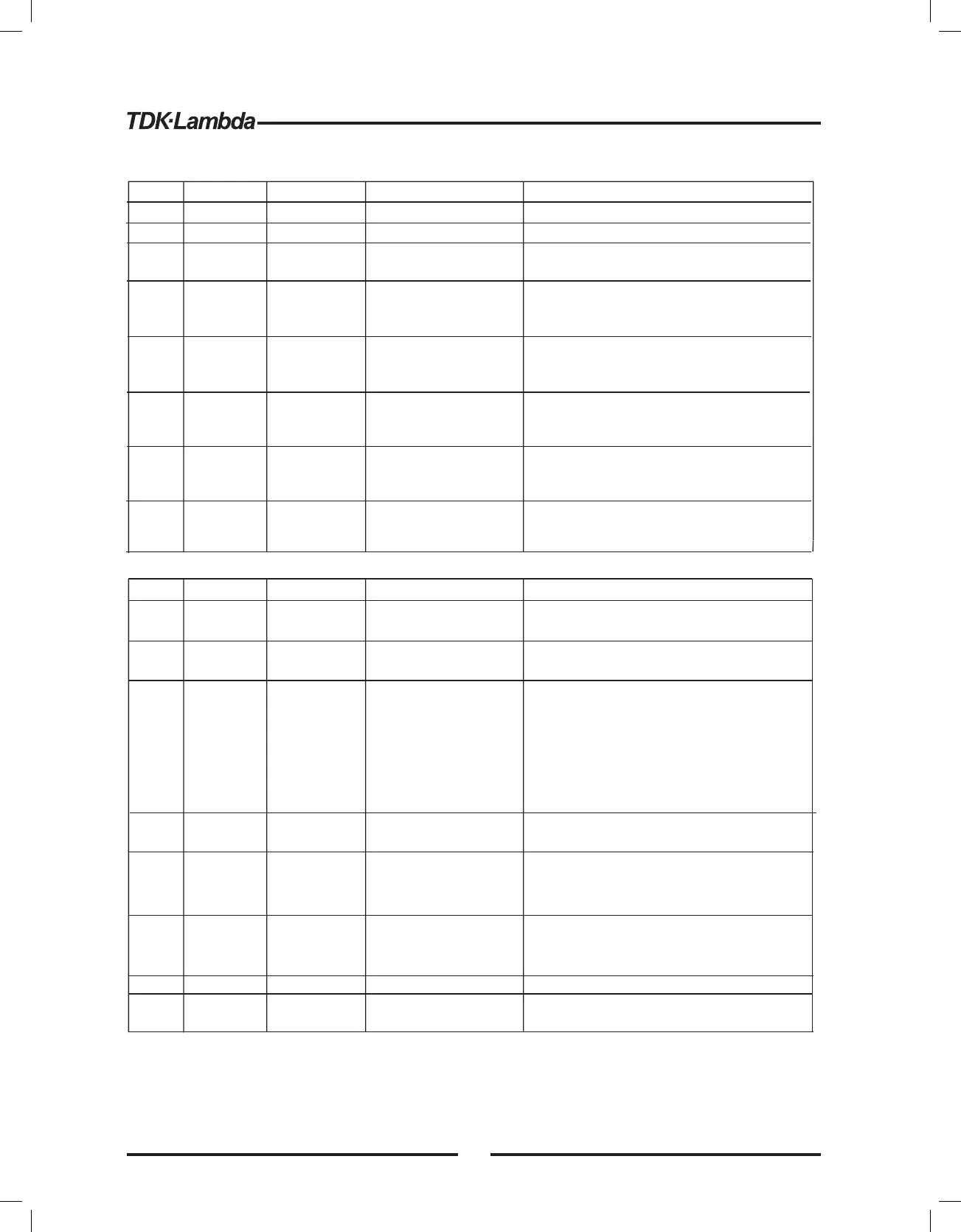

Refer to Tables 7-10 to 7-13 for details of the Enable and Event registers.

The Fault Enable Register is set to the enable faults SRQs.

1.Fault Enable Register

2.Fault Event Register

The Fault Event will setabit ifacondition occurs and it is enabled. The register is cleared when

FEVE?, CLS or RST commands are received.

Table 7-10: Fault Enable Register

BIT

Enable

bit name

Fault symbol

0 (LSB)

1

2

3

4

5

6

7(MSB)

Spare bit

AC Fail

Over Temperature

Foldback

Over Voltage

Shut Off

Output Off

Enable

SPARE

AC

OTP

FOLD

OVP

SO

OFF

ENA

Bit Set condition

Bit reset condition

User command:

"FENA nn" where

nn is hexadecimal

User command: "FENA nn"

where nn is hexadecimal (if

nn="00", no fault SRQs will

be generated).

Table 7-11: Fault Event Register

0 (LSB)

1

2

3

4

5

6

7(MSB)

Spare bit

AC Fail

Over Temperature

Foldback

Over Voltage

Shut Off

Output Off

Enable

SPARE

AC

OTP

FOLD

OVP

SO

OFF

ENA

Entire Event Register is

cleared when user sends

"FEVE?" command to read

the register.

"CLS" and power-up also

clear the Fault Event

Register. (The Fault Event

Register is not cleared by

RST)

BIT

Event

bit name

Fault symbol

Bit Set condition

Bit reset condition

Fault condition

occurs and it is

enabled.

The fault can set

a bit, but when

the fault clears

the bit remains

set.

58

Loading...

Loading...