AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

www.ti.com

SPRS717H –OCTOBER 2011–REVISED MAY 2015

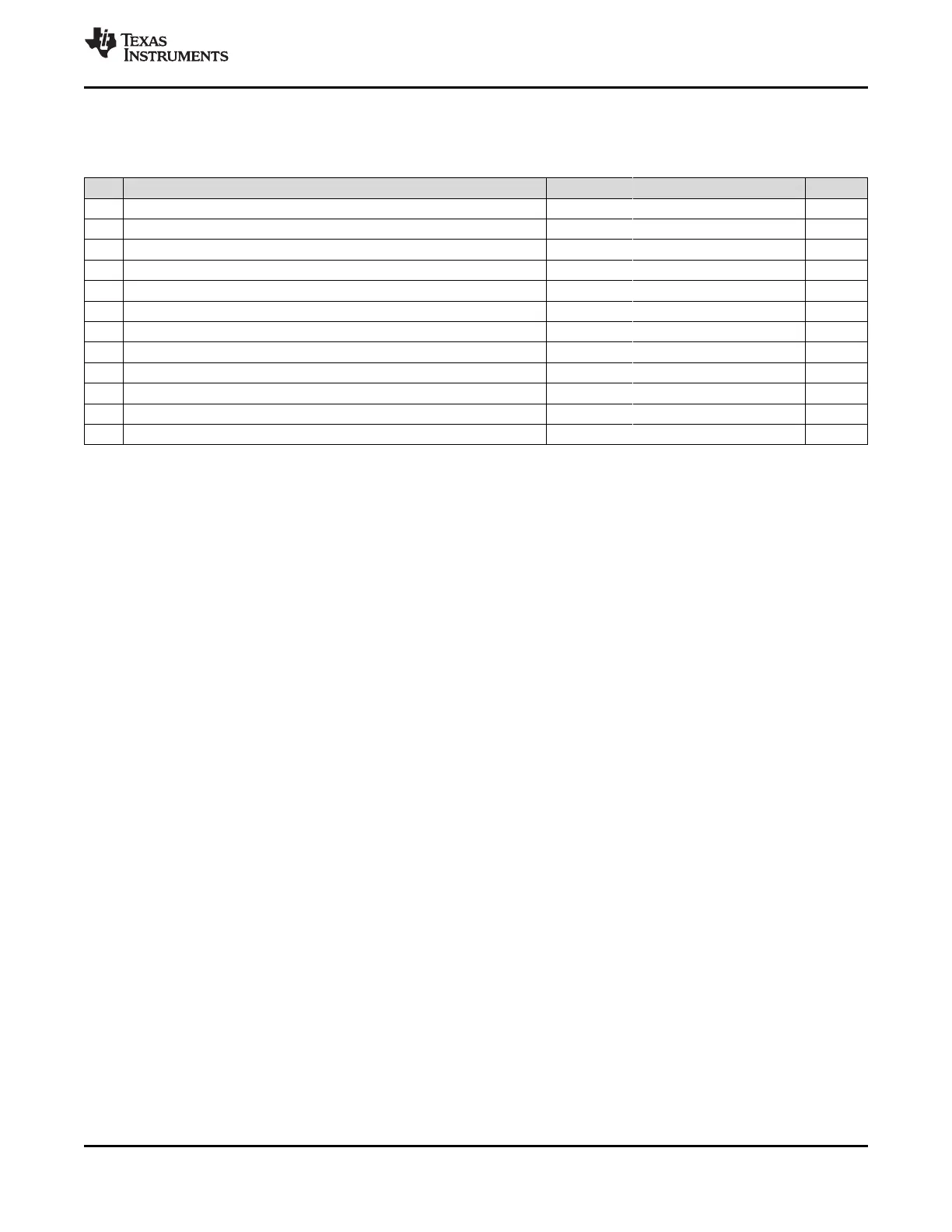

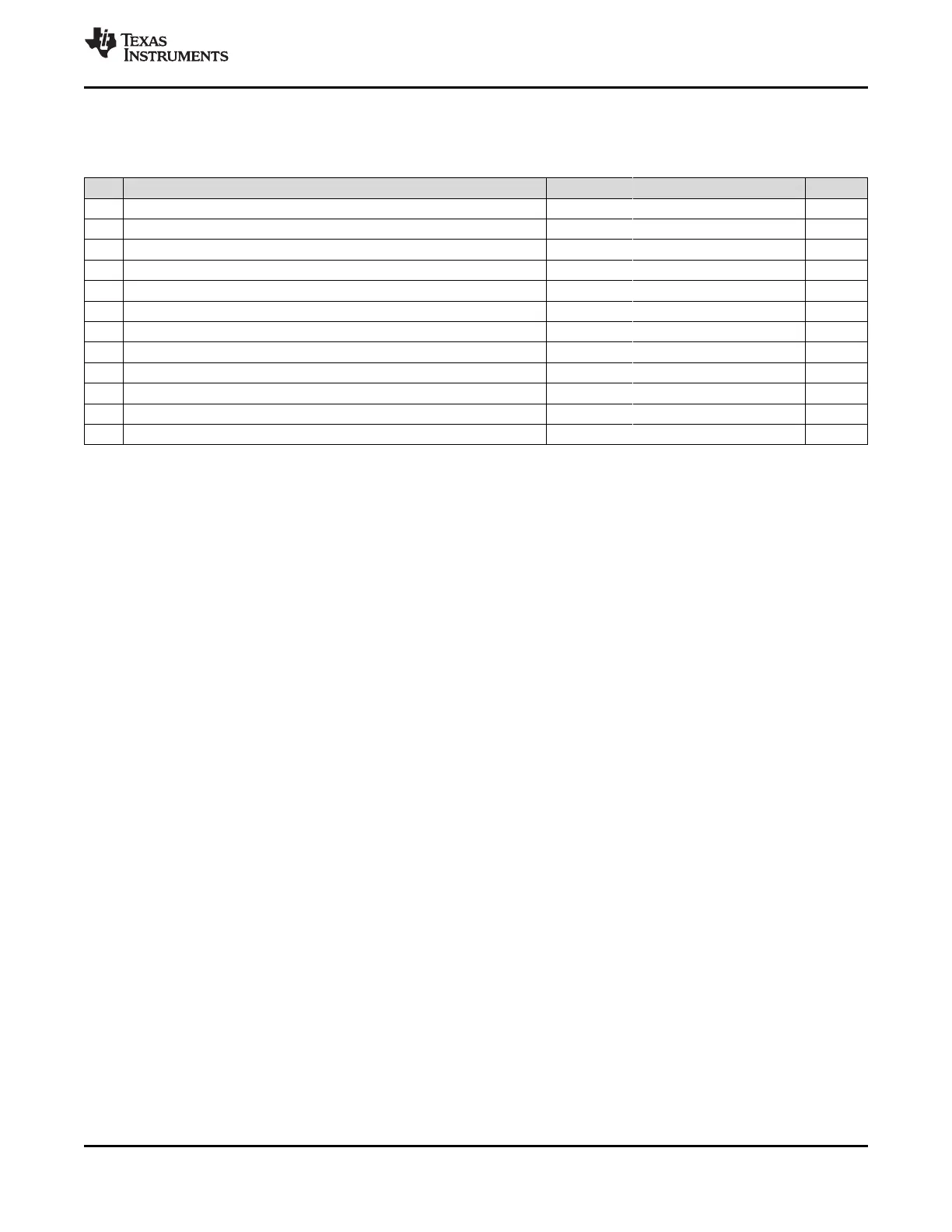

Complete stackup specifications are provided in Table 7-46.

Table 7-46. PCB Stackup Specifications

(1)

NO. PARAMETER MIN TYP MAX UNIT

1 PCB routing and plane layers 4

2 Signal routing layers 2

3 Full ground layers under DDR2 routing region 1

4 Number of ground plane cuts allowed within DDR2 routing region 0

5 Full VDDS_DDR power reference layers under DDR2 routing region 1

6 Number of layers between DDR2 routing layer and reference ground plane 0

7 PCB routing feature size 4 mils

8 PCB trace width, w 4 mils

9 PCB BGA escape via pad size

(2)

18 20 mils

10 PCB BGA escape via hole size

(2)

10 mils

11 Single-ended impedance, Zo

(3)

50 75 Ω

12 Impedance control

(4)(5)

Zo-5 Zo Zo+5 Ω

(1) For the DDR2 device BGA pad size, see the DDR2 device manufacturer documentation.

(2) A 20-10 via may be used if enough power routing resources are available. An 18-10 via allows for more flexible power routing to the

AM335x device.

(3) Zo is the nominal singled-ended impedance selected for the PCB.

(4) This parameter specifies the AC characteristic impedance tolerance for each segment of a PCB signal trace relative to the chosen Zo

defined by the single-ended impedance parameter.

(5) Tighter impedance control is required to ensure flight time skew is minimal.

Copyright © 2011–2015, Texas Instruments Incorporated Peripheral Information and Timings 163

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...