AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

www.ti.com

SPRS717H –OCTOBER 2011–REVISED MAY 2015

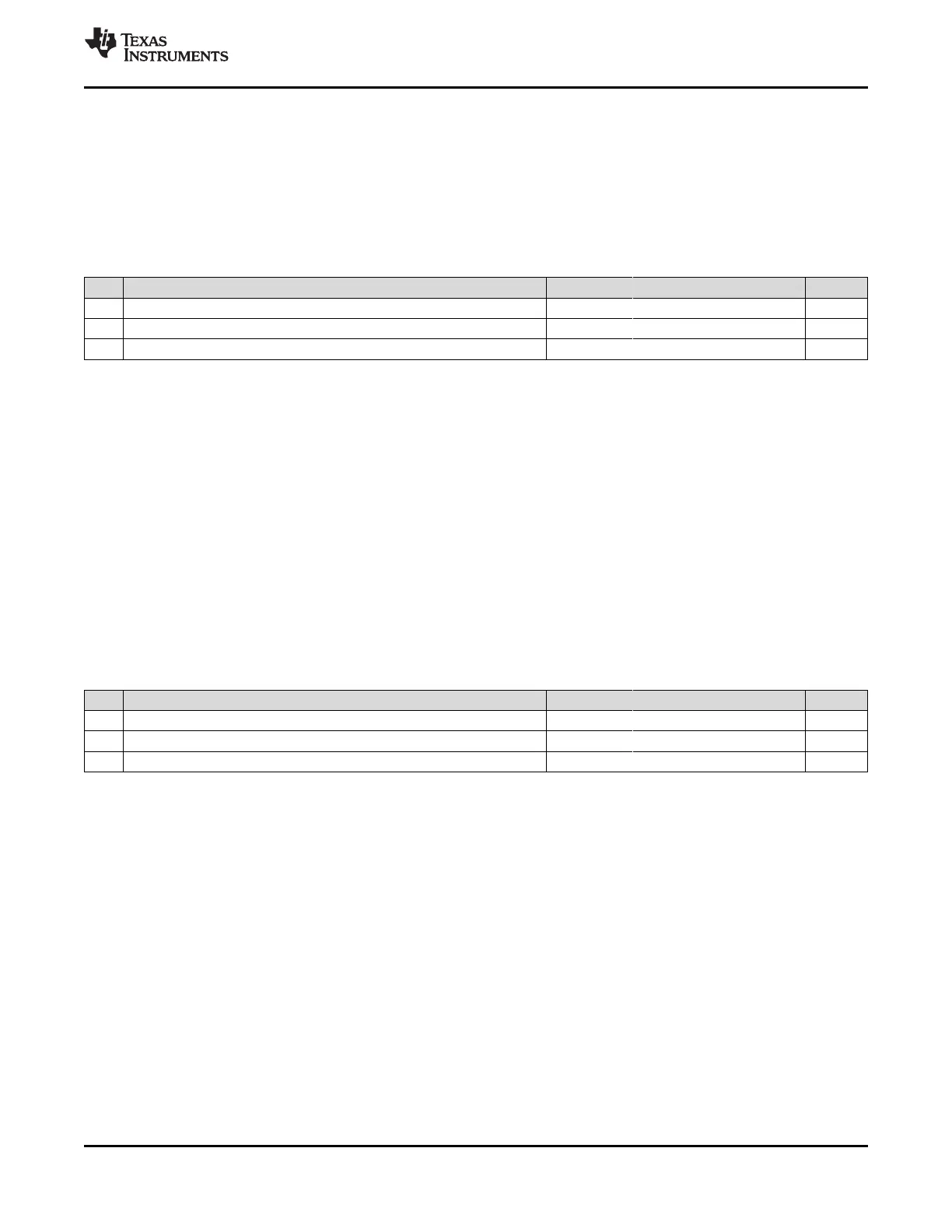

7.7.2.2.2.9 DDR2 Signal Termination

Signal terminations are required on the CK and ADDR_CTRL net class signals. Serial terminations should

be used on the CK and ADDR_CTRL lines and is the preferred termination scheme. On-device

terminations (ODTs) are required on the DQS[x] and DQ[x] net class signals. They should be enabled to

ensure signal integrity. Table 7-52 shows the specifications for the series terminators. Placement of serial

terminations for ADDR_CTRL net class signals should be close to the AM335x device.

Table 7-52. DDR2 Signal Terminations

NO. PARAMETER MIN TYP MAX UNIT

1 CK net class

(1)

0 10 Ω

2 ADDR_CTRL net class

(1)(2)(3)

0 22 Zo

(4)

Ω

3 DQS0, DQS1, DQ0, and DQ1 net classes

(5)

N/A N/A Ω

(1) Only series termination is permitted.

(2) Series termination values larger than typical only recommended to address EMI issues.

(3) Series termination values should be uniform across net class.

(4) Zo is the DDR2 PCB trace characteristic impedance.

(5) No external termination resistors are allowed and ODT must be used for these net classes.

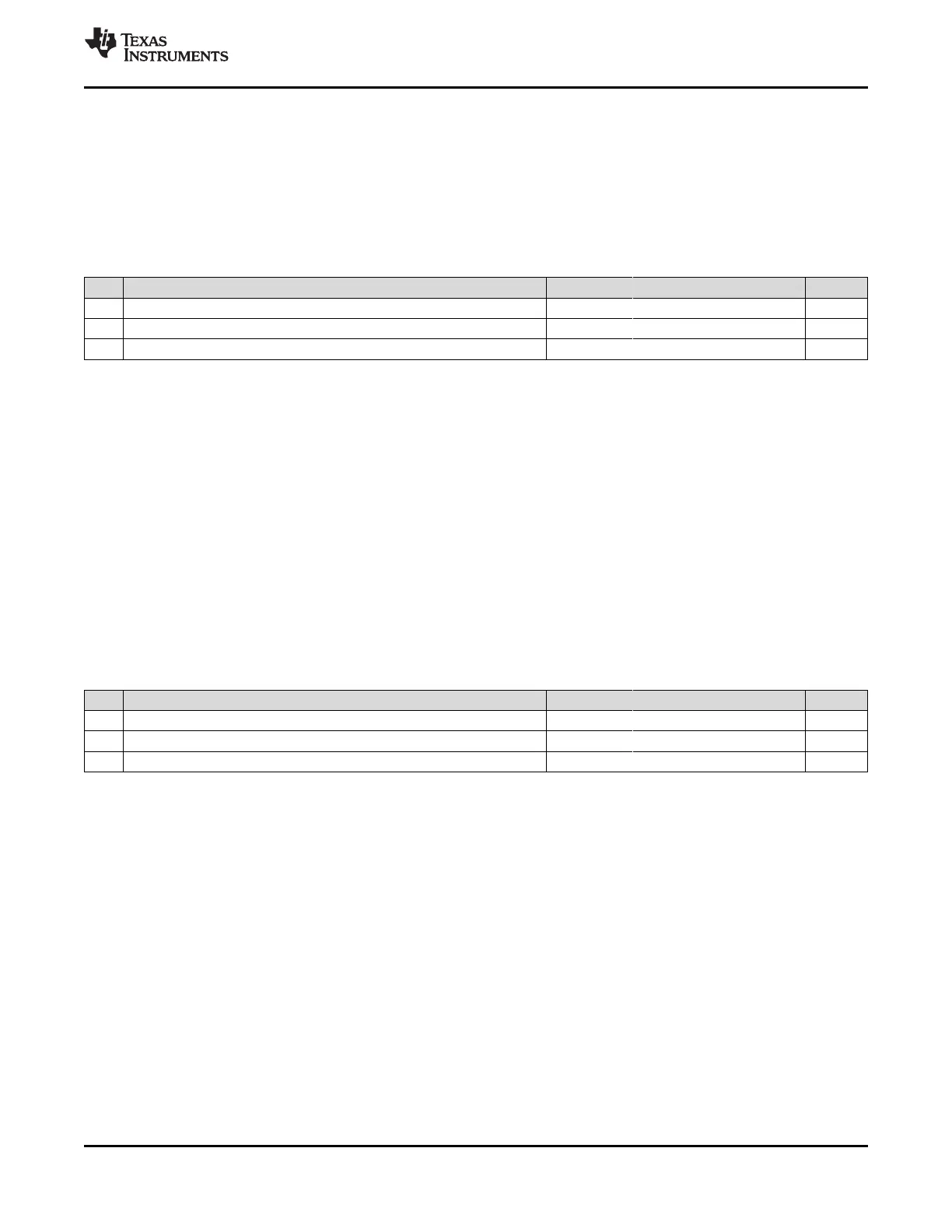

If the DDR2 interface is operated at a lower frequency (<200-MHz clock rate), on-device terminations are

not specifically required for the DQS[x] and DQ[x] net class signals and serial terminations for the CK and

ADDR_CTRL net class signals are not mandatory. System designers may evaluate the need for serial

terminators for EMI and overshoot reduction. Placement of serial terminations for DQS[x] and DQ[x] net

class signals should be determined based on PCB analysis. Placement of serial terminations for

ADDR_CTRL net class signals should be close to the AM335x device. Table 7-53 shows the

specifications for the serial terminators in such cases.

Table 7-53. Lower-Frequency DDR2 Signal Terminations

NO. PARAMETER MIN TYP MAX UNIT

1 CK net class

(1)

0 22 Zo

(2)

Ω

2 ADDR_CTRL net class

(1)(3)(4)

0 22 Zo

(2)

Ω

3 DQS0, DQS1, DQ0, and DQ1 net classes 0 22 Zo

(2)

Ω

(1) Only series termination is permitted.

(2) Zo is the DDR2 PCB trace characteristic impedance.

(3) Series termination values larger than typical only recommended to address EMI issues.

(4) Series termination values should be uniform across net class.

Copyright © 2011–2015, Texas Instruments Incorporated Peripheral Information and Timings 167

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...