10

MMC[x]_CLK (Output)

MMC[x]_CMD (Output)

MMC[x]_DAT[7:0] (Outputs)

11

RMII[x]_REFCLK

(Input)

5

7

6

8

9

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

SPRS717H –OCTOBER 2011–REVISED MAY 2015

www.ti.com

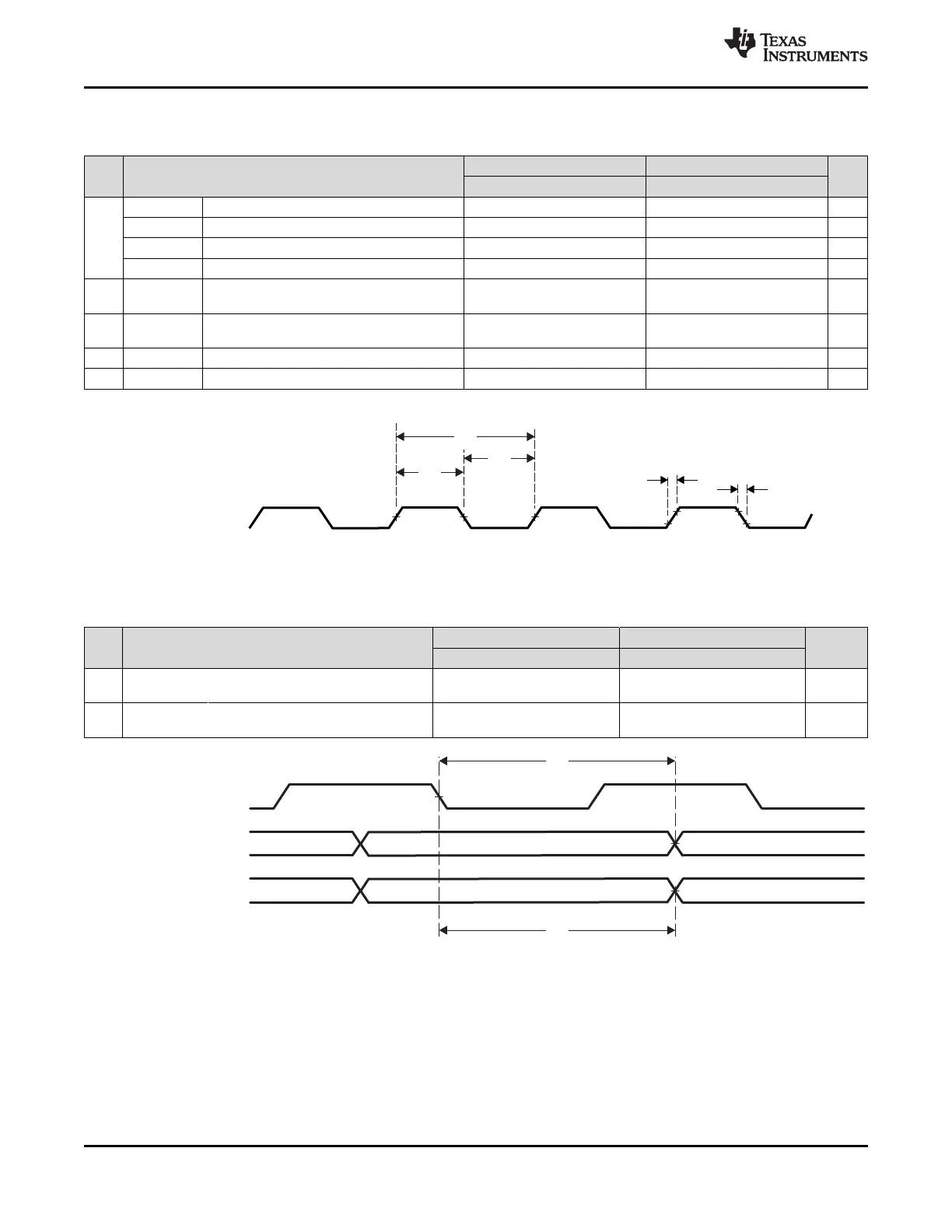

Table 7-88. Switching Characteristics for MMC[x]_CLK

(see Figure 7-93)

STANDARD MODE HIGH-SPEED MODE

NO. PARAMETER UNIT

MIN TYP MAX MIN TYP MAX

ƒ

op(CLK)

Operating frequency, MMC_CLK 24 48 MHz

t

cop(CLK)

Operating period: MMC_CLK 41.7 20.8 ns

5

f

id(CLK)

Identification mode frequency, MMC_CLK 400 400 kHz

t

cid(CLK)

Identification mode period: MMC_CLK 2500 2500 ns

(0.5 × P) – (0.5 × P) –

6 t

w(CLKL)

Pulse duration, MMC_CLK low ns

t

f(CLK)

(1)

t

f(CLK)

(1)

(0.5 × P) – (0.5 × P) –

7 t

w(CLKH)

Pulse duration, MMC_CLK high ns

t

r(CLK)

(1)

t

r(CLK)

(1)

8 t

r(CLK)

Rise time, all signals (10% to 90%) 2.2 2.2 ns

9 t

f(CLK)

Fall time, all signals (10% to 90%) 2.2 2.2 ns

(1) P = MMC_CLK period

Figure 7-93. MMC[x]_CLK Timing

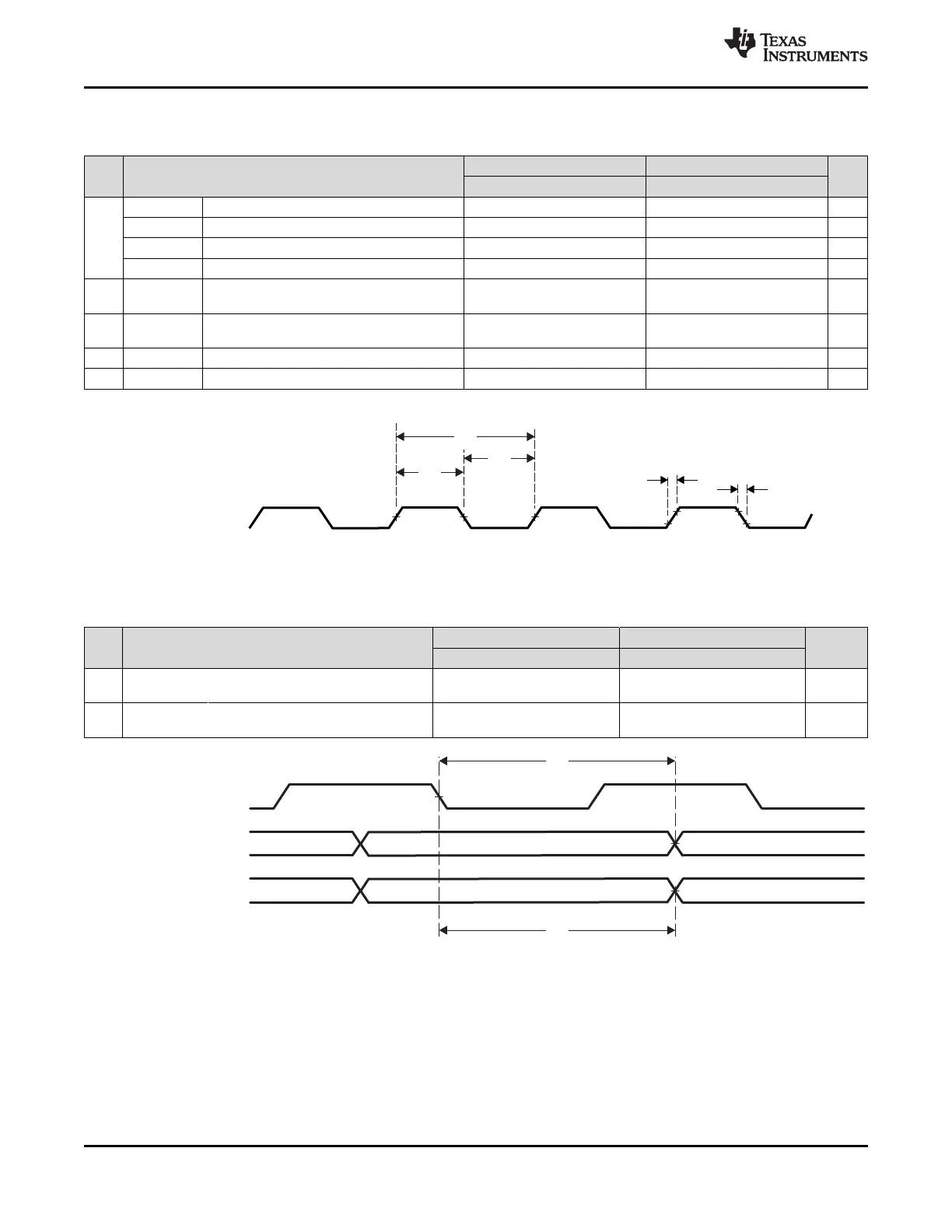

Table 7-89. Switching Characteristics for MMC[x]_CMD and MMC[x]_DAT[7:0] – Standard Mode

(see Figure 7-94)

OPP100 OPP50

NO. PARAMETER UNIT

MIN TYP MAX MIN TYP MAX

Delay time, MMC_CLK falling clock

10 t

d(CLKL-CMD)

–4 14 –4 17.5 ns

edge to MMC_CMD transition

Delay time, MMC_CLK falling clock

11 t

d(CLKL-DAT)

–4 14 –4 17.5 ns

edge to MMC_DATx transition

Figure 7-94. MMC[x]_CMD and MMC[x]_DAT[7:0] Output Timing—Standard Mode

222 Peripheral Information and Timings Copyright © 2011–2015, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...