AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

SPRS717H –OCTOBER 2011–REVISED MAY 2015

www.ti.com

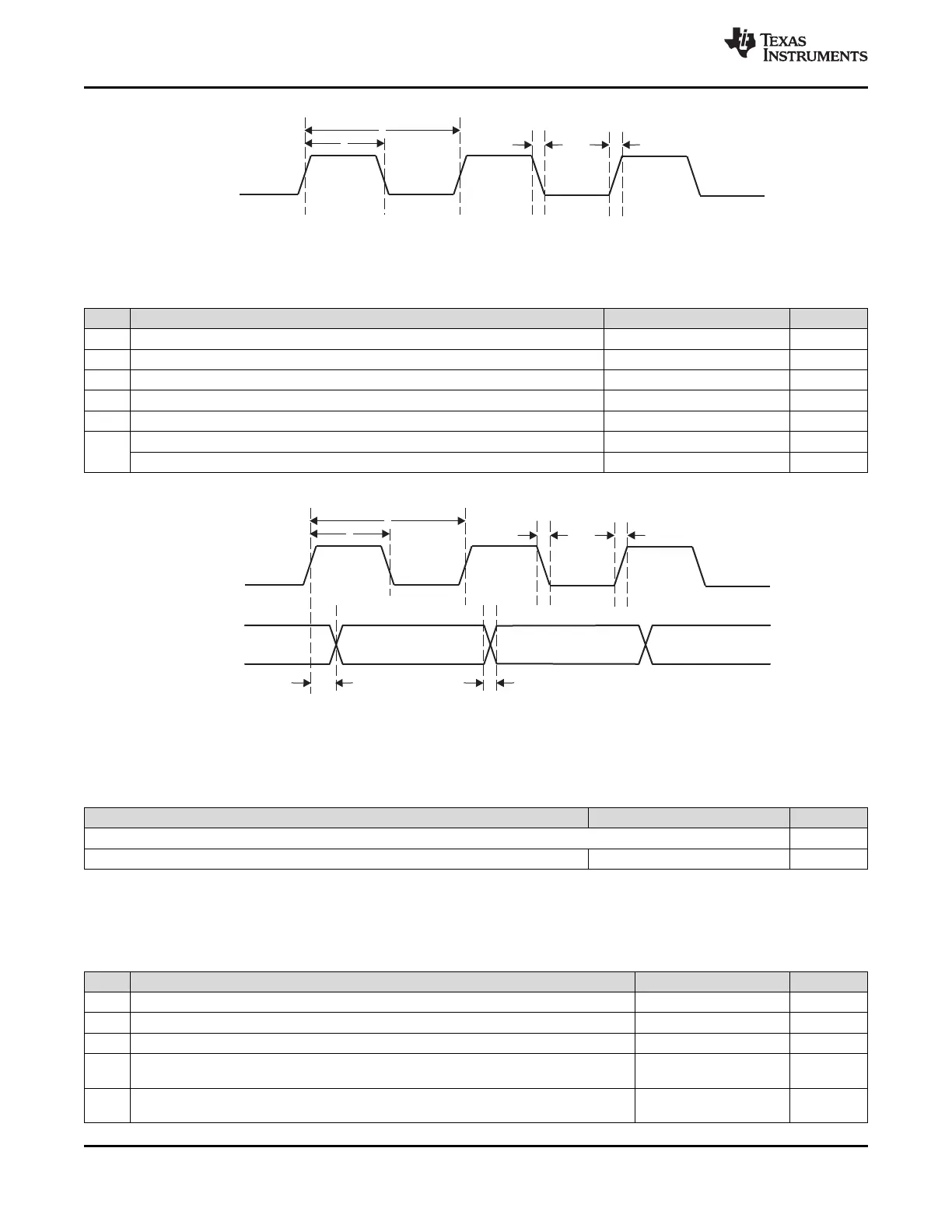

Figure 7-100. PRU-ICSS PRU Shift In Timing

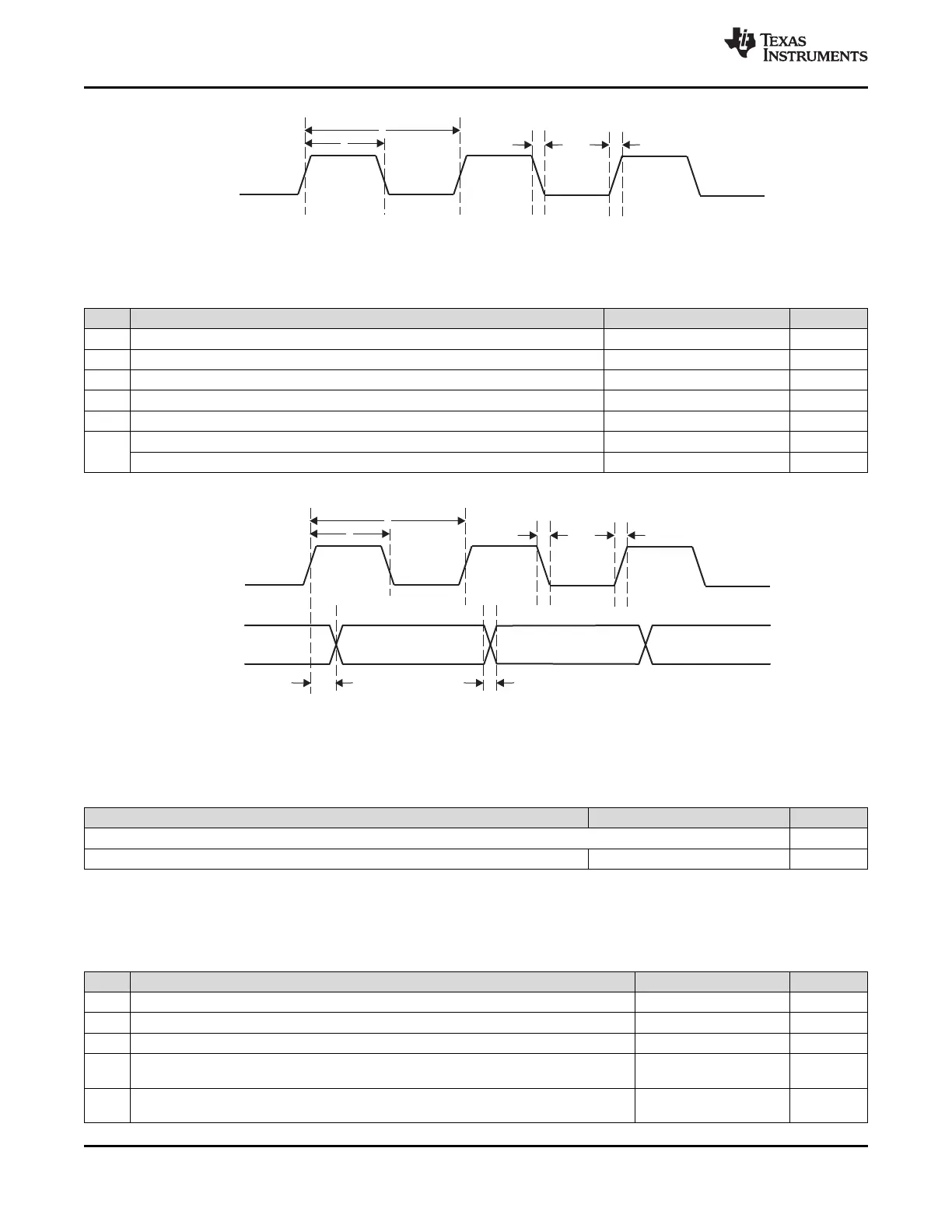

Table 7-96. PRU-ICSS PRU Switching Requirements - Shift Out Mode

(see Figure 7-101)

NO. MIN MAX UNIT

1 t

c(CLOCKOUT)

Cycle time, CLOCKOUT 10.00 ns

2 t

w(CLOCKOUT)

Pulse width, CLOCKOUT 0.45 × P

(1)

0.55 × P

(1)

ns

3 t

r(CLOCKOUT)

Rising time, CLOCKOUT 1.00 3.00 ns

4 t

f(CLOCKOUT)

Falling time, CLOCKOUT 1.00 3.00 ns

5 t

d(CLOCKOUT-DATAOUT)

Delay time, CLOCKOUT to DATAOUT valid 0.00 3.00 ns

6 t

r(DATAOUT)

Rising time, DATAOUT 1.00 3.00 ns

t

f(DATAOUT)

Falling time, DATAOUT 1.00 3.00 ns

(1) P = L3_CLK (PRU-ICSS ocp clock) period.

Figure 7-101. PRU-ICSS PRU Shift Out Timing

7.14.2 PRU-ICSS EtherCAT (PRU-ICSS ECAT)

Table 7-97. PRU-ICSS ECAT Timing Conditions

PARAMETER MIN MAX UNIT

Output Condition

C

load

Capacitive load for each bus line 30 pF

7.14.2.1 PRU-ICSS ECAT Electrical Data and Timing

Table 7-98. PRU-ICSS ECAT Timing Requirements – Input Validated with LATCH_IN

(see Figure 7-102)

NO. MIN MAX UNIT

1 t

w(EDIO_LATCH_IN)

Pulse width, EDIO_LATCH_IN 100.00 ns

2 t

r(EDIO_LATCH_IN)

Rising time, EDIO_LATCH_IN 1.00 3.00 ns

3 t

f(EDIO_LATCH_IN)

Falling time, EDIO_LATCH_IN 1.00 3.00 ns

4 t

su(EDIO_DATA_IN-

Setup time, EDIO_DATA_IN valid before EDIO_LATCH_IN 20.00 ns

EDIO_LATCH_IN)

active edge

5 t

h(EDIO_LATCH_IN-

Hold time, EDIO_DATA_IN valid after EDIO_LATCH_IN active 20.00 ns

EDIO_DATA_IN)

edge

226 Peripheral Information and Timings Copyright © 2011–2015, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...