3

2

Start

Bit

Data Bits

UART_TXD

5

Data Bits

Bit

Start

4

UART_RXD

1

MII_TXCLK (input)

MII_TXD[3:0],

MII_TXEN (outputs)

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

SPRS717H –OCTOBER 2011–REVISED MAY 2015

www.ti.com

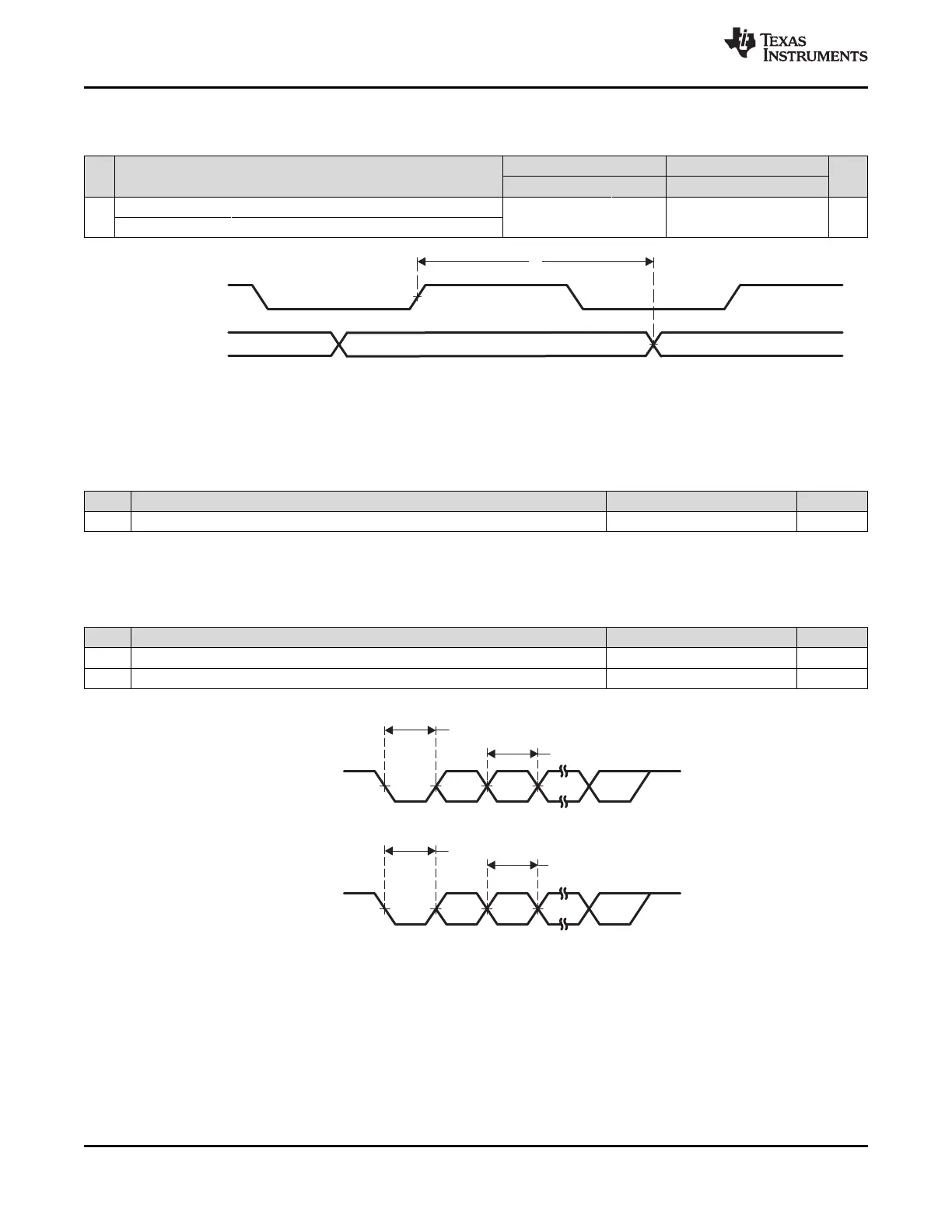

Table 7-110. PRU-ICSS MII_RT Switching Characteristics - MII_TXD[3:0] and MII_TXEN

(see Figure 7-112)

10 Mbps 100 Mbps

NO

UNIT

.

MIN TYP MAX MIN TYP MAX

t

d(TX_CLK-TXD)

Delay time, TX_CLK high to TXD[3:0] valid

1 5 25 5 25 ns

t

d(TX_CLK-TX_EN)

Delay time, TX_CLK to TX_EN valid

Figure 7-112. PRU-ICSS MII_TXD[3:0], MII_TXEN Timing

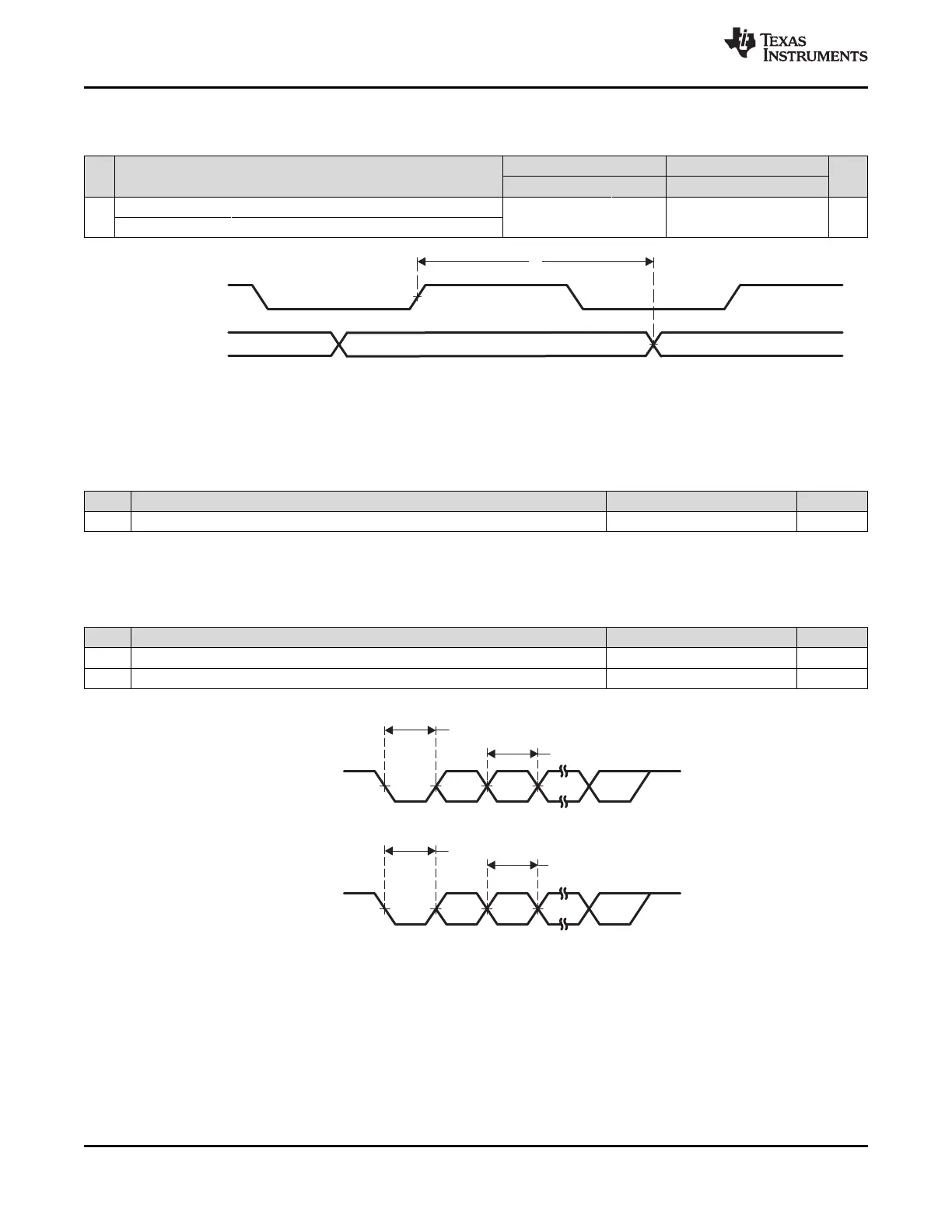

7.14.4 PRU-ICSS Universal Asynchronous Receiver Transmitter (PRU-ICSS UART)

Table 7-111. Timing Requirements for PRU-ICSS UART Receive

(see Figure 7-113)

NO. MIN MAX UNIT

3 t

w(RX)

Pulse duration, receive start, stop, data bit 0.96U

(1)

1.05U

(1)

ns

(1) U = UART baud time = 1/programmed baud rate.

Table 7-112. Switching Characteristics Over Recommended Operating Conditions for PRU-ICSS UART

Transmit

(see Figure 7-113)

NO. PARAMETER MIN MAX UNIT

1 ƒ

baud(baud)

Maximum programmable baud rate 0 12 MHz

2 t

w(TX)

Pulse duration, transmit start, stop, data bit U – 2

(1)

U + 2

(1)

ns

(1) U = UART baud time = 1/programmed baud rate.

Figure 7-113. PRU-ICSS UART Timing

232 Peripheral Information and Timings Copyright © 2011–2015, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...