MII_MRCLK (Input)

1

2

MII_RXD[3:0],

MII_RXDV,

MII_RXER (Inputs)

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

www.ti.com

SPRS717H –OCTOBER 2011–REVISED MAY 2015

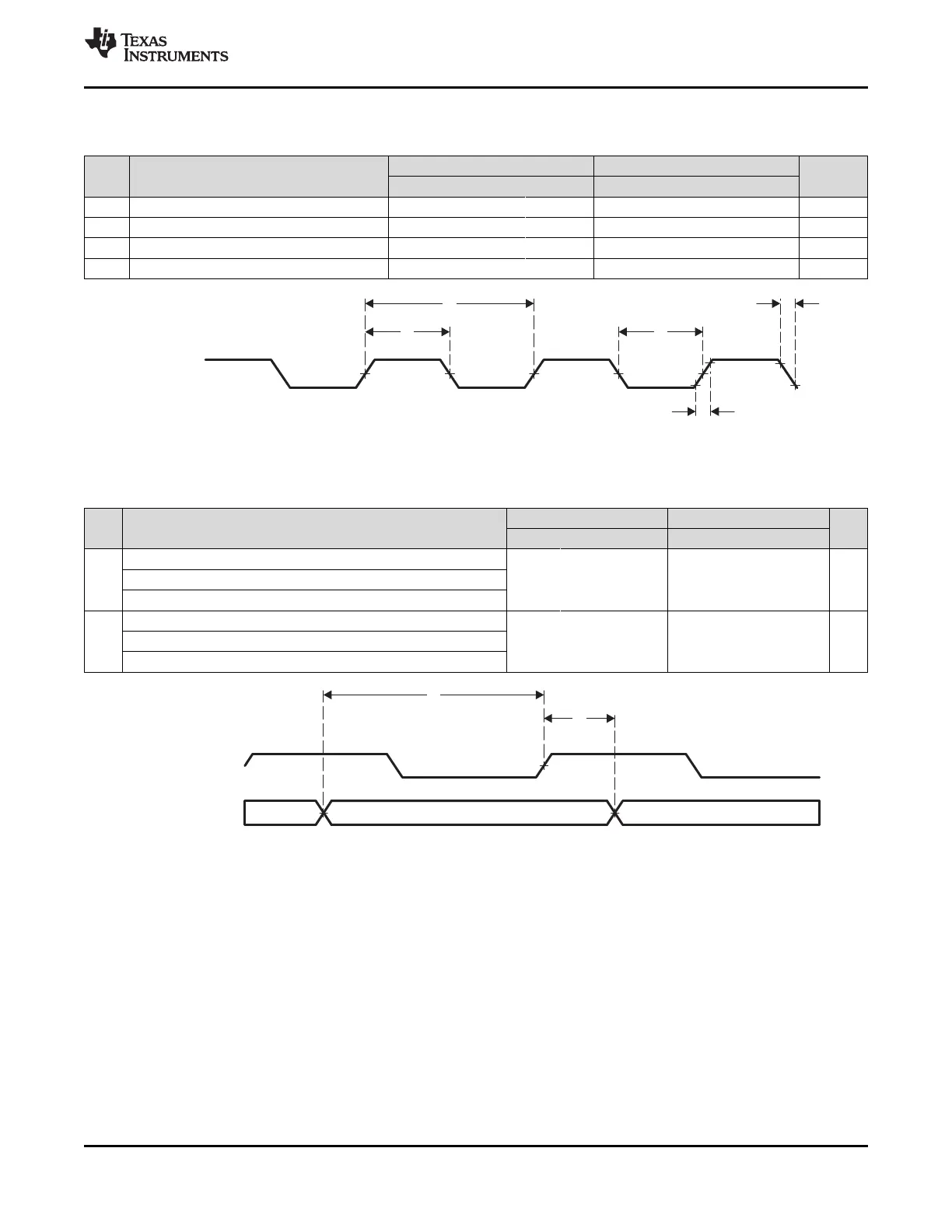

Table 7-108. PRU-ICSS MII_RT Timing Requirements - MII[x]_TXCLK

(see Figure 7-110)

10 Mbps 100 Mbps

NO. UNIT

MIN TYP MAX MIN TYP MAX

1 t

c(TX_CLK)

Cycle time, TX_CLK 399.96 400.04 39.996 40.004 ns

2 t

w(TX_CLKH)

Pulse duration, TX_CLK high 140 260 14 26 ns

3 t

w(TX_CLKL)

Pulse duration, TX_CLK low 140 260 14 26 ns

4 t

t(TX_CLK)

Transition time, TX_CLK 3 3 ns

Figure 7-110. PRU-ICSS MII_TXCLK Timing

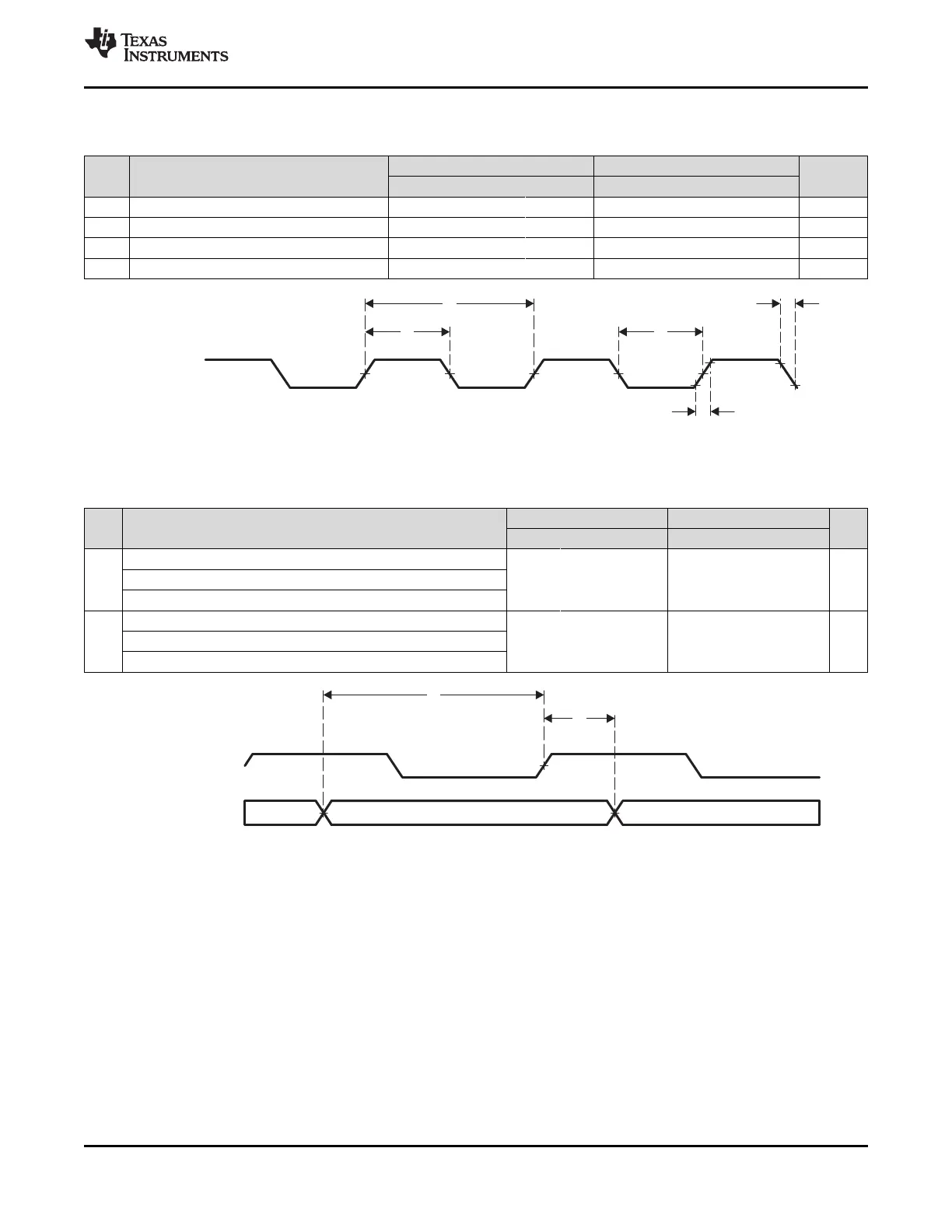

Table 7-109. PRU-ICSS MII_RT Timing Requirements - MII_RXD[3:0], MII_RXDV, and MII_RXER

(see Figure 7-111)

10 Mbps 100 Mbps

NO. UNIT

MIN TYP MAX MIN TYP MAX

t

su(RXD-RX_CLK)

Setup time, RXD[3:0] valid before RX_CLK

1 t

su(RX_DV-RX_CLK)

Setup time, RX_DV valid before RX_CLK 8 8 ns

t

su(RX_ER-RX_CLK)

Setup time, RX_ER valid before RX_CLK

t

h(RX_CLK-RXD)

Hold time RXD[3:0] valid after RX_CLK

2 t

h(RX_CLK-RX_DV)

Hold time RX_DV valid after RX_CLK 8 8 ns

t

h(RX_CLK-RX_ER)

Hold time RX_ER valid after RX_CLK

Figure 7-111. PRU-ICSS MII_RXD[3:0], MII_RXDV, and MII_RXER Timing

Copyright © 2011–2015, Texas Instruments Incorporated Peripheral Information and Timings 231

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...