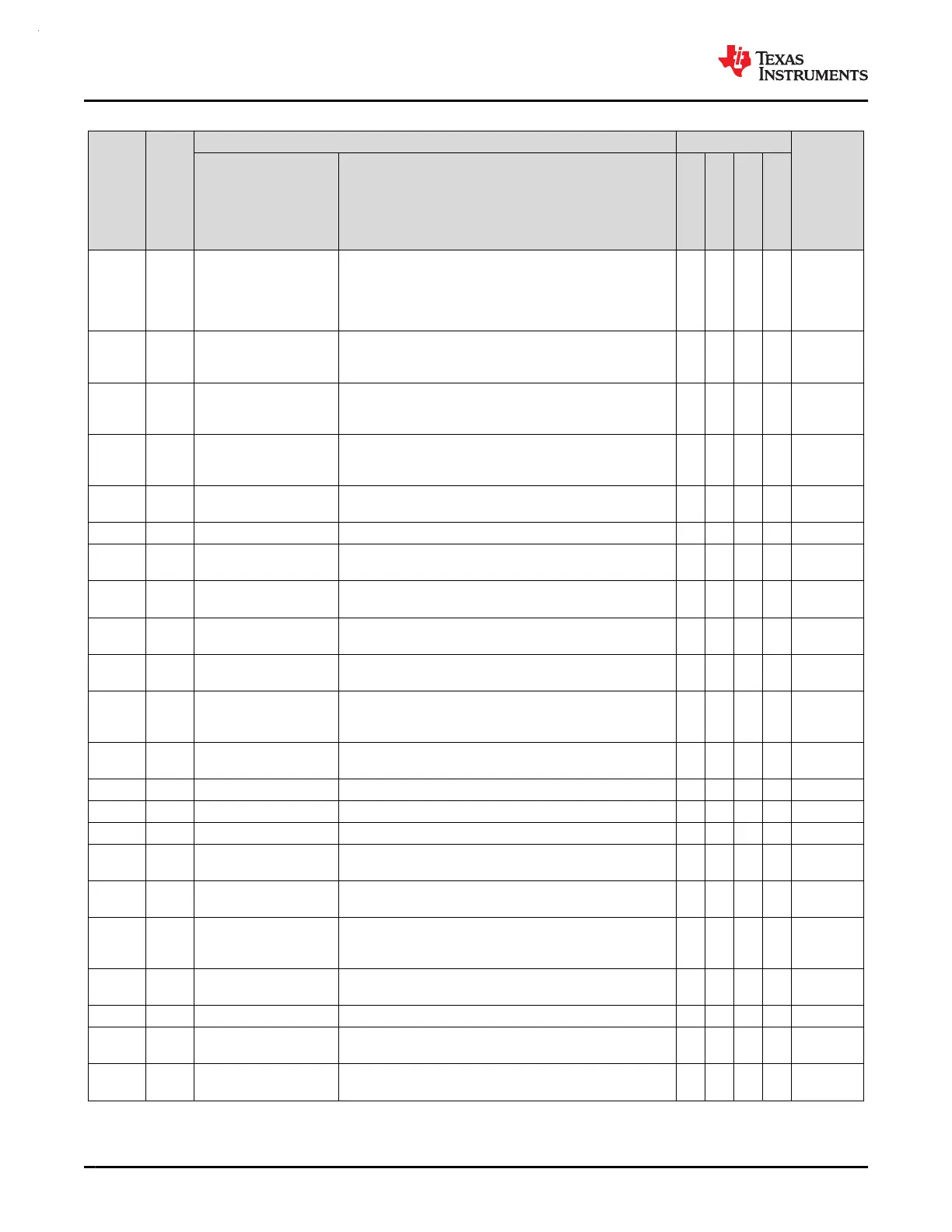

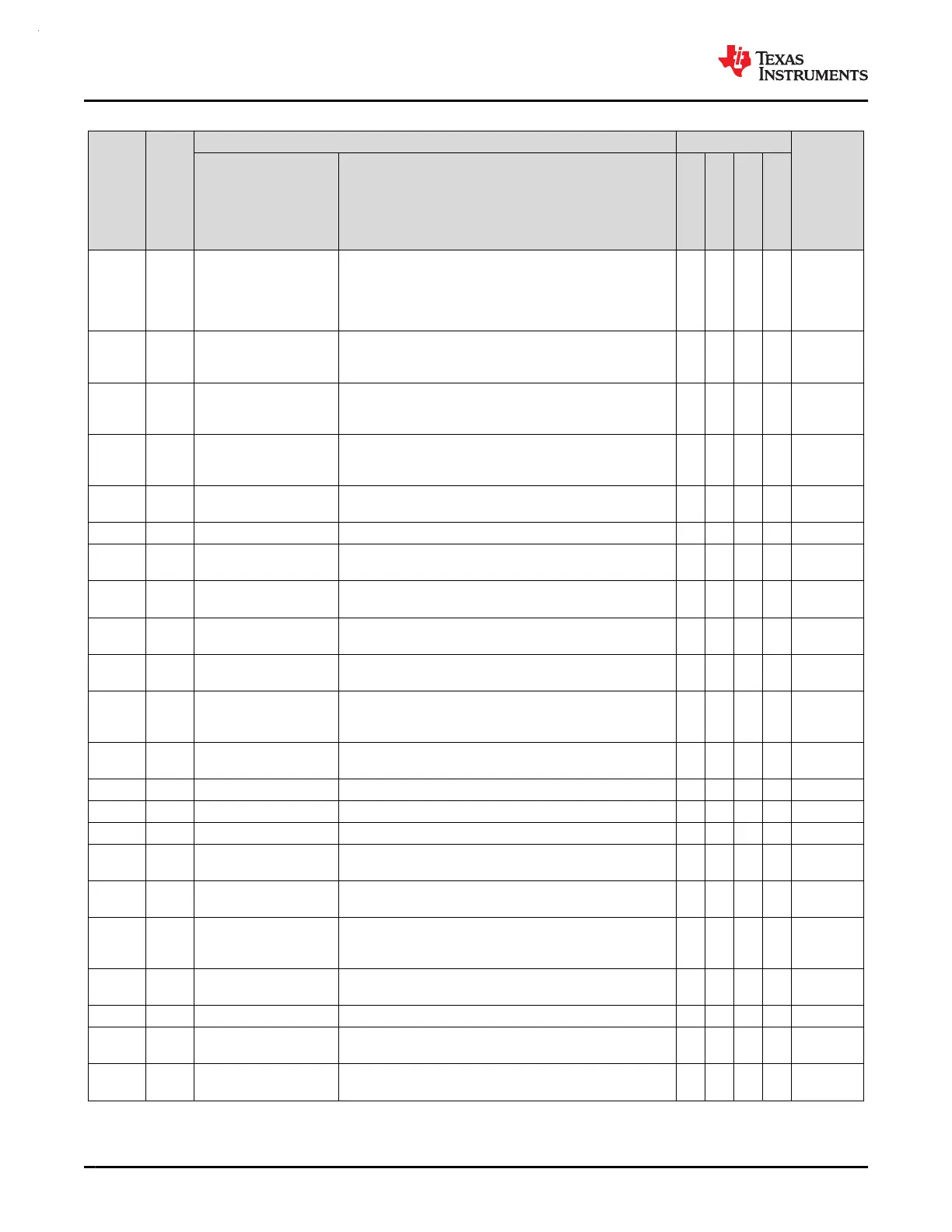

Table 6-1. Pin Attributes (continued)

PINCMx

PIN

NAME

SIGNAL NAMES PIN NUMBER

IO

STRUCTU

RE

ANALOG DIGITAL [PIN FUNCTION]

(1)

64 LQFP

48 LQFP, VQFN

32 VQFN

28 VSSOP

37

PA15 A1_0 / DAC_OUT /

OPA0_IN2+ /

OPA1_IN2+/

COMP0_IN3+ /

COMP1_IN3+

UART0_RTS [2] / SPI1_CS2 [3] / I2C1_SCL [4] / TIMA1_C0

[5] / TIMG8_IDX [6] / TIMA1_C0N [7] / TIMA0_C2 [8]

8 30 19 18 Standard

38

PA16

A1_1 / OPA1_OUT

COMP2_OUT [2] / SPI1_POCI [3] / I2C1_SDA [4] /

TIMA1_C1 [5] / TIMA1_C1N [6] / TIMA0_C2N [7] / FCC_IN

[8]

9 31 20 19 Standard

39

PA17

A1_2 / OPA1_IN1- /

COMP0_IN1-

UART1_TX [2] / SPI1_SCK [3] / I2C1_SCL [4] / TIMA0_C3

[5] / TIMG7_C0 [6] / TIMA1_C0 [7]

10 32 21 20

Standard

with

wake

(2)

40

PA18 A1_3 / OPA1_IN1+ /

COMP0_IN1+ /

GPAMP_IN-

UART1_RX [2] / SPI1_PICO [3] / I2C1_SDA [4] /

TIMA0_C3N [5] / TIMG7_C1 [6] / TIMA1_C1 [7]

11 33 22 21

Standard

with

wake

(2)

41

PA19

SWDIO [2] 12 34 23 22

High-

Speed

42 PA20 SWCLK [2] 13 35 24 23 Standard

43

PB17

A1_4 / COMP1_IN2-

UART2_TX [2] / SPI0_PICO [3] / SPI1_CS1 [4] / TIMA1_C0

[5] / TIMA0_C2 [6]

14 36 – – Standard

44

PB18

A1_5 / COMP1_IN2+

UART2_RX [2] / SPI0_SCK [3] / SPI1_CS2 [4] / TIMA1_C1

[5] / TIMA0_C2N [6]

15 37 – – Standard

45

PB19 A1_6 / COMP2_IN1+ /

OPA1_IN0+

COMP2_OUT [2] / SPI0_POCI [3] / TIMG8_C1 [4] /

UART0_CTS [5] / TIMG7_C1 [6]

16 38 – – Standard

46

PA21 A1_7 / COMP2_IN1- /

VREF-

UART2_TX [2] / TIMG8_C0 [3] / UART1_CTS [4] /

TIMA0_C0 [5] / TIMG6_C0 [6]

17 39 25 24 Standard

47

PA22

A0_7 / GPAMP_OUT /

OPA0_OUT

UART2_RX [2] / TIMG8_C1 [3] / UART1_RTS [4] /

TIMA0_C1 [5] / CLK_OUT [6] / TIMA0_C0N [7] / TIMG6_C1

[8]

18 40 26 25 Standard

48

PB20

A0_6 / OPA1_IN0-

SPI0_CS2 [2] / SPI1_CS0 [3] / TIMA0_C2 [4] / TIMG12_C0

[5] / TIMA_FAL1 [6] / TIMA0_C1 [7] / TIMA1_C1N [8]

19 41 – – Standard

49 PB21 COMP2_IN0+ SPI1_POCI [2] / TIMG8_C0 [3] 20 – – – Standard

50 PB22 COMP2_IN0- SPI1_PICO [2] / TIMG8_C1 [3] 21 – – – Standard

51 PB23 SPI1_SCK [2] / COMP0_OUT [3] / TIMA_FAL0 [4] 22 – – – Standard

52

PB24

A0_5 / COMP1_IN1+

SPI0_CS3 [2] / SPI0_CS1 [3] / TIMA0_C3 [4] / TIMG12_C1

[5] / TIMA0_C1N [6] / TIMA1_C0N [7]

23 42 – – Standard

53

PA23

COMP1_IN1- / VREF+

UART2_TX [2] / SPI0_CS3 [3] / TIMA0_C3 [4] / TIMG0_C0

[5] / UART3_CTS [6] / TIMG7_C0 [7]/ TIMG8_C0 [8]

24 43 27 26 Standard

54

PA24

A0_3 / OPA0_IN1-

UART2_RX [2] / SPI0_CS2 [3] / TIMA0_C3N [4] /

TIMG0_C1 [5] / UART3_RTS [6] / TIMG7_C1 [7] /

TIMA1_C1 [8]

25 44 28 27 Standard

55

PA25

A0_2 / OPA0_IN1+

UART3_RX [2] / SPI1_CS3 [3] / TIMG12_C1 [4] /

TIMA0_C3 [5] / TIMA0_C1N [6]

26 45 29 28 Standard

56 PB25 A0_4 UART0_CTS [2] / SPI0_CS0 [3] / TIMA_FAL2 [4] 27 – – – Standard

57

PB26

COMP1_IN0+

UART0_RTS [2] / SPI0_CS1 [3] / TIMA0_C3 [4] /

TIMG6_C0 [5] / TIMA1_C0 [6]

28 – – – Standard

58

PB27

COMP1_IN0-

COMP2_OUT [2] / SPI1_CS1 [3] / TIMA0_C3N [4] /

TIMG6_C1 [5] / TIMA1_C1 [6]

29 – – – Standard

MSPM0G3507, MSPM0G3506, MSPM0G3505

SLASEX6A – FEBRUARY 2023 – REVISED JUNE 2023

www.ti.com

14 Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: MSPM0G3507 MSPM0G3506 MSPM0G3505

Loading...

Loading...