RM46L852

www.ti.com

SPNS185 –SEPTEMBER 2012

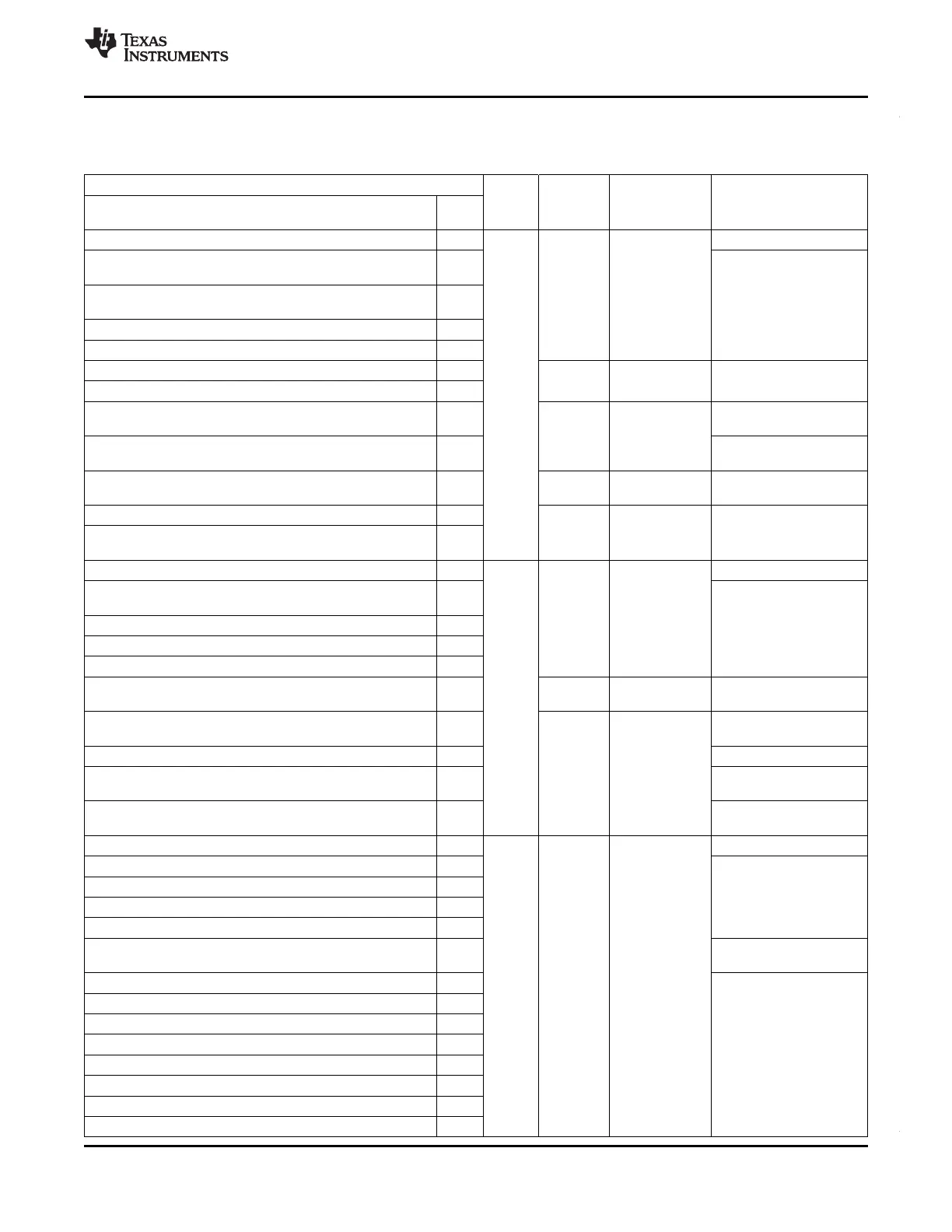

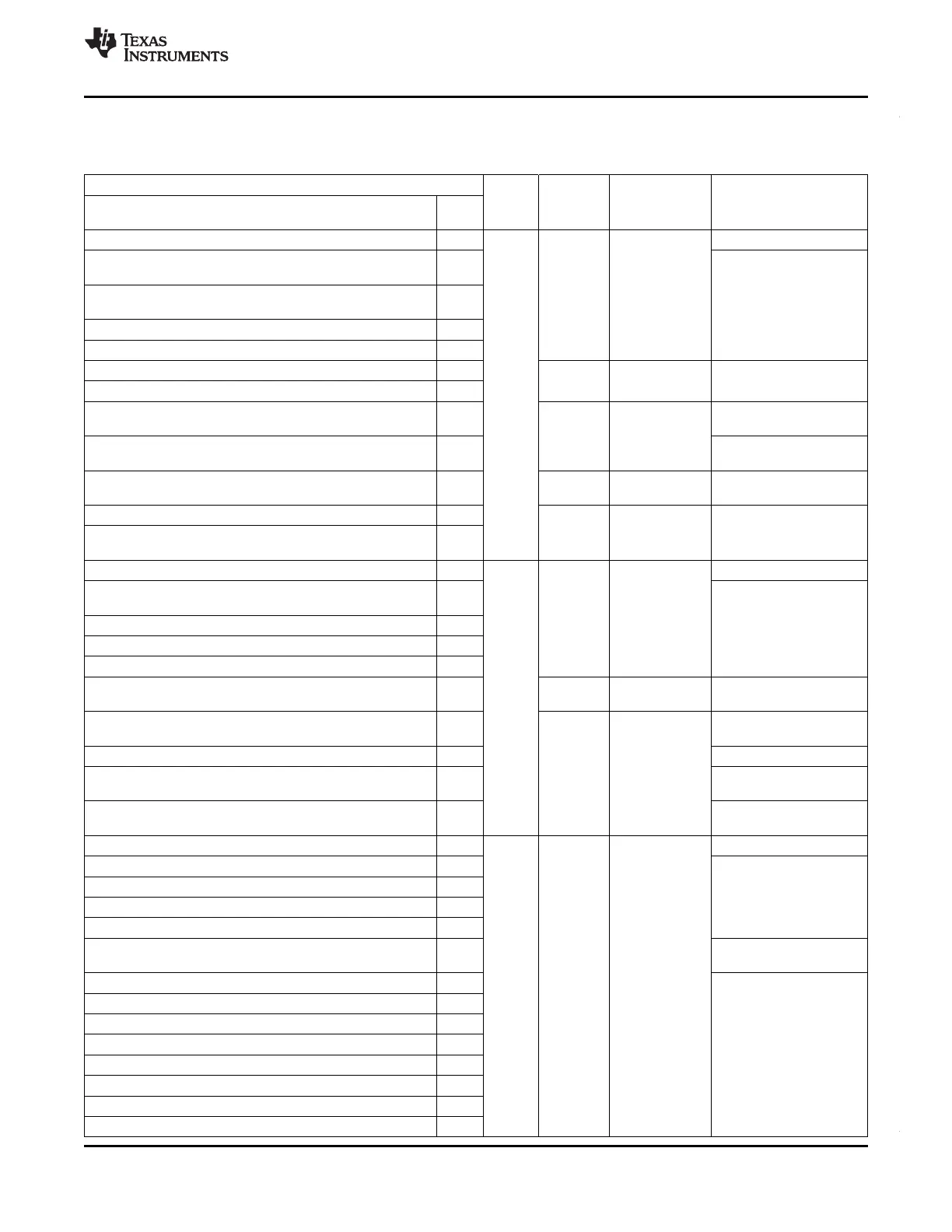

2.3.2.12 Multi-Buffered Serial Peripheral Interface Modules (MibSPI)

Table 2-36. ZWT Multi-Buffered Serial Peripheral Interface Modules (MibSPI)

Terminal Signal Default Pull Type Description

Type Pull State

Signal Name 337

ZWT

MIBSPI1CLK F18 I/O Pull Up Programmable, MibSPI1 clock, or GIO

20uA

MIBSPI1NCS[0]/MIBSPI1SOMI[1]/MII_TXD[2]/ R2 MibSPI1 chip select, or

USB1.RCV GIO

MIBSPI1NCS[1]/N2HET1[17]/MII_COL/ F3

USB1.SUSPEND /EQEP1S

MIBSPI1NCS[2]/N2HET1[19]/MDIO G3

MIBSPI1NCS[3]/N2HET1[21] J3

N2HET1[15]/MIBSPI1NCS[4] N1 Pull Down Programmable, MibSPI1 chip select, or

20uA GIO

N2HET1[24]/MIBSPI1NCS[5]/MII_RXD[0]/RMII_RXD[0] P1

MIBSPI1NENA/N2HET1[23]/MII_RXD[2]/ G19 Pull Up Programmable, MibSPI1 enable, or GIO

USB1.VP/ECAP4 20uA

MIBSPI1SIMO F19 MibSPI1 slave-in master-

out, or GIO

N2HET1[08]/MIBSPI1SIMO[1]/MII_TXD[3]/USB1.OverCurrent E18 Pull Down Programmable, MibSPI1 slave-in master-

20uA out, or GIO

MIBSPI1SOMI G18 Pull Up Programmable, MibSPI1 slave-out master-

20uA in, or GIO

MIBSPI1NCS[0]/MIBSPI1SOMI[1]/MII_TXD[2]/ECAP6/ R2

USB1.RCV

MIBSPI3CLK/AWM1_EXT_SEL[1]/EQEP1A V9 I/O Pull Up Programmable, MibSPI3 clock, or GIO

20uA

MIBSPI3NCS[0]/AD2EVT/GIOB[2]/EQEP1I/N2HET2_PIN_nD V10 MibSPI3 chip select, or

IS GIO

MIBSPI3NCS[1]/N2HET1[25]/MDCLK V5

MIBSPI3NCS[2]/I2C_SDA/N2HET1[27]/nTZ2 B2

MIBSPI3NCS[3]/I2C_SCL/N2HET1[29]/nTZ1 C3

N2HET1[11]/MIBSPI3NCS[4]/N2HET2[18]/ E3 Pull Down Programmable, MibSPI3 chip select, or

USB2.OverCurrent/USB_FUNC.VBUSI/EPWM1SYNCO 20uA GIO

MIBSPI3NENA/MIBSPI3NCS[5]/N2HET1[31]/EQEP1B W9 Pull Up Programmable, MibSPI3 chip select, or

20uA GIO

MIBSPI3NENA/MIBSPI3NCS[5]/N2HET1[31]/EQEP1B W9 MibSPI3 enable, or GIO

MIBSPI3SIMO/AWM1_EXT_SEL[0]/ECAP3 W8 MibSPI3 slave-in master-

out, or GIO

MIBSPI3SOMI/AWM1_EXT_ENA/ECAP2 V8 MibSPI3 slave-out master-

in, or GIO

MIBSPI5CLK/MII_TXEN/RMII_TXEN H19 I/O Pull Up Programmable, MibSPI5 clock, or GIO

20uA

MIBSPI5NCS[0]/EPWM4A E19 MibSPI5 chip select, or

GIO

MIBSPI5NCS[1] B6

MIBSPI5NCS[2] W6

MIBSPI5NCS[3] T12

MIBSPI5NENAMII_RXD[3]/ H18 MibSPI5 enable, or GIO

USB1.VM/MIBSPI5SOMI[1]/ECAP5

MIBSPI5SIMO[0]/MII_TXD[1]/RMII_TXD[1] J19 MibSPI5 slave-in master-

out, or GIO

MIBSPI5SIMO[1] E16

MIBSPI5SIMO[2] H17

MIBSPI5SIMO[3] G17

MIBSPI5SOMI[0]/MII_TXD[0]/RMII_TXD[0] J18

MIBSPI5SOMI[1] E17

MIBSPI5SOMI[2] H16

MIBSPI5SOMI[3] G16

Copyright © 2012, Texas Instruments Incorporated Device Package and Terminal Functions 33

Submit Documentation Feedback

Loading...

Loading...