IOMUX

EPWM1SYNCO

ECAP1

ECAP

6

ECAP1INTn

ECAP1ENCLK

VCLK4,SYS_nRST

ECAP2ENCLK

ECAP

2/3/4/5

VCLK4,SYS_nRST

ECAP2INTn

ECAP6INTn

VBus32

VBus32

VIM

VIM

VIM

ECAP1

ECAP1SYNCI

ECAP1SYNCO

ECAP2SYNCI

ECAP2SYNCO

ECAP2

ECAP6ENCLK

VCLK4,SYS_nRST

VBus32

ECAP6

RM46L852

SPNS185 –SEPTEMBER 2012

www.ti.com

5.2 Enhanced Capture Modules (eCAP)

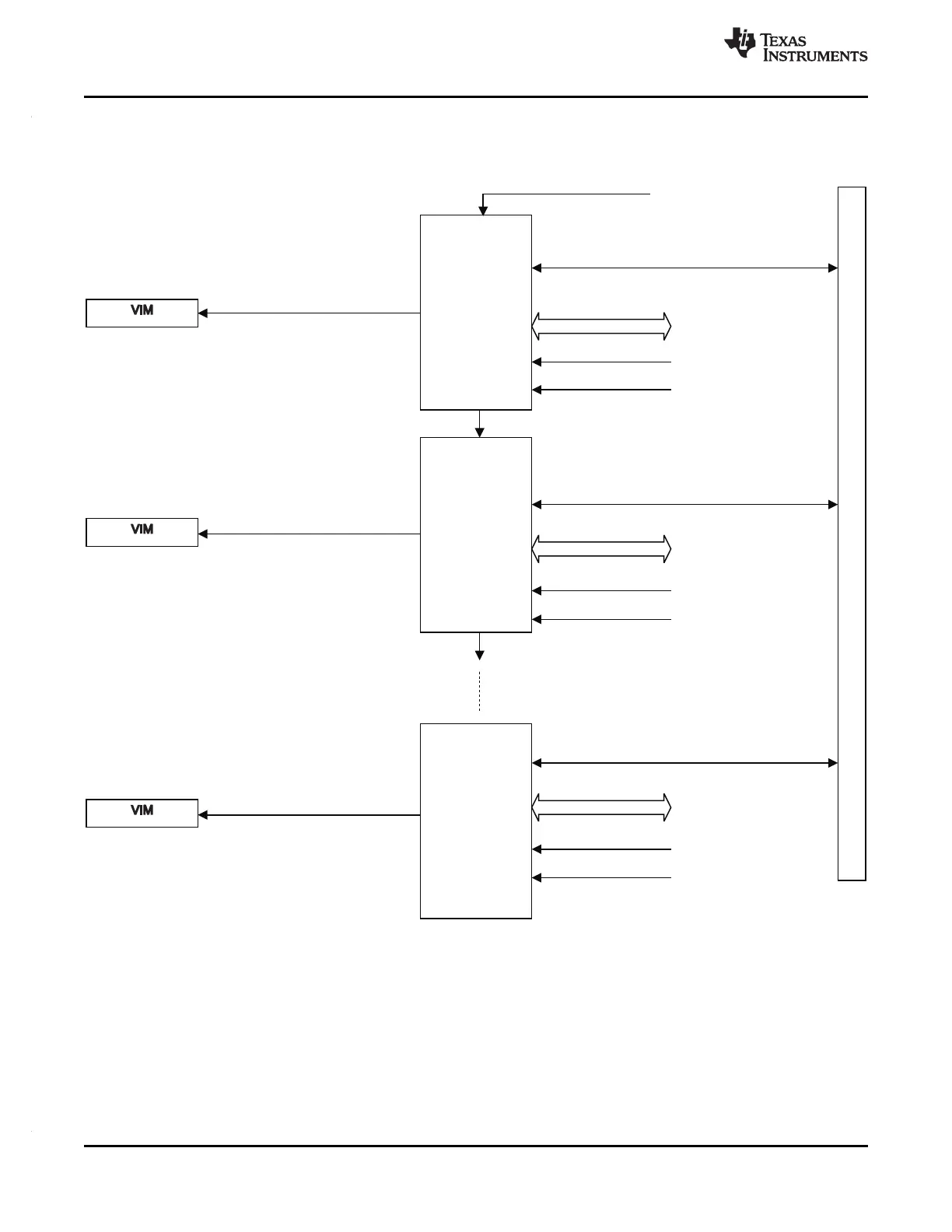

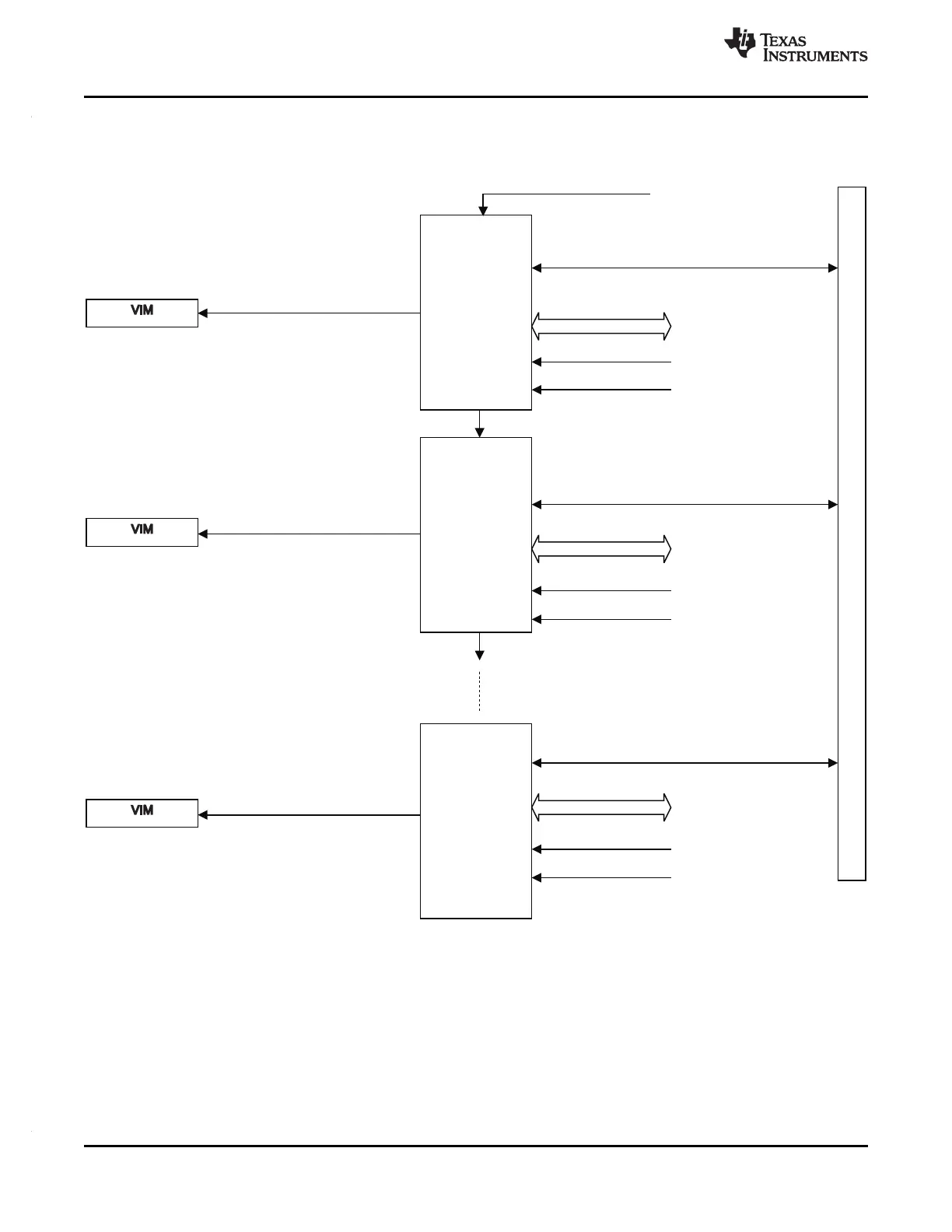

Figure 5-3 shows how the eCAP modules are interconnected on this microcontroller.

Figure 5-3. eCAP Module Connections

5.2.1 Clock Enable Control for eCAPx Modules

Each of the ECAPx modules have a clock enable (ECAPxENCLK). These signals need to be generated

from a device-level control register. When SYS_nRST is active low, the clock enables are ignored and the

ECAPx logic is clocked so that it can reset to a proper state. When SYS_nRST goes in-active high, the

state of clock enable is respected.

122 Peripheral Information and Electrical Specifications Copyright © 2012, Texas Instruments Incorporated

Submit Documentation Feedback

Loading...

Loading...