RM46L852

www.ti.com

SPNS185 –SEPTEMBER 2012

4.10 Flash Memory

4.10.1 Flash Memory Configuration

Flash Bank: A separate block of logic consisting of 1 to 16 sectors. Each flash bank normally has a

customer-OTP and a TI-OTP area. These flash sectors share input/output buffers, data paths, sense

amplifiers, and control logic.

Flash Sector: A contiguous region of flash memory which must be erased simultaneously due to physical

construction constraints.

Flash Pump: A charge pump which generates all the voltages required for reading, programming, or

erasing the flash banks.

Flash Module: Interface circuitry required between the host CPU and the flash banks and pump module.

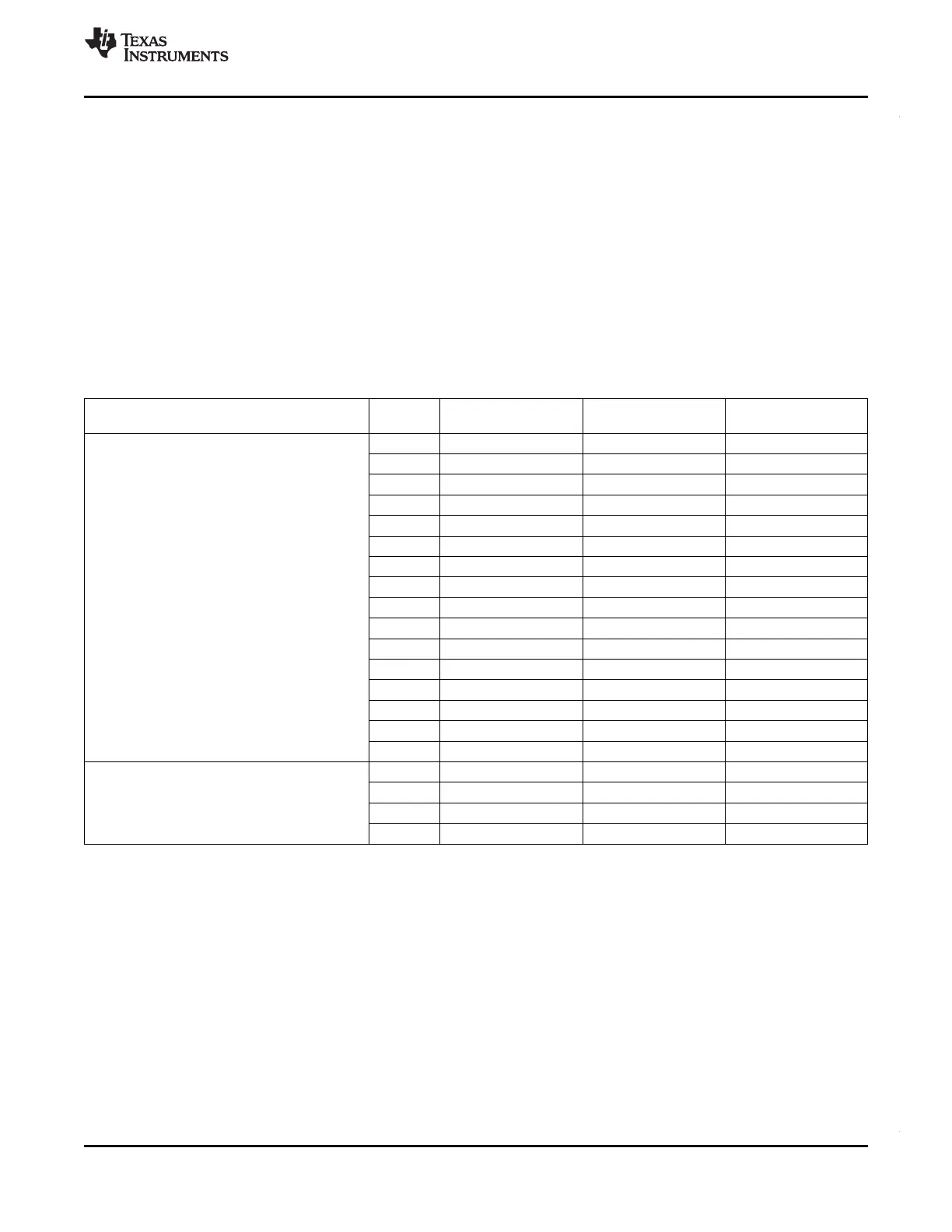

Table 4-23. Flash Memory Banks and Sectors

Memory Arrays (or Banks) Sector Segment Low Address High Address

No.

BANK0 (1.25MBytes) 0 16K Bytes 0x0000_0000 0x0000_3FFF

1 16K Bytes 0x0000_4000 0x0000_7FFF

2 16K Bytes 0x0000_8000 0x0000_BFFF

3 16K Bytes 0x0000_C000 0x0000_FFFF

4 16K Bytes 0x0001_0000 0x0001_3FFF

5 16K Bytes 0x0001_4000 0x0001_7FFF

6 32K Bytes 0x0001_8000 0x0001_FFFF

7 128K Bytes 0x0002_0000 0x0003_FFFF

8 128K Bytes 0x0004_0000 0x0005_FFFF

9 128K Bytes 0x0006_0000 0x0007_FFFF

10 128K Bytes 0x0008_0000 0x0009_FFFF

11 128K Bytes 0x000A_0000 0x000B_FFFF

12 128K Bytes 0x000C_0000 0x000D_FFFF

13 128K Bytes 0x000E_0000 0x000F_FFFF

14 128K Bytes 0x0010_0000 0x0011_FFFF

15 128K Bytes 0x0012_0000 0x0013_FFFF

BANK7 (64kBytes) for EEPROM emulation 0 16K Bytes 0xF020_0000 0xF020_3FFF

1 16K Bytes 0xF020_4000 0xF020_7FFF

2 16K Bytes 0xF020_8000 0xF020_BFFF

3 16K Bytes 0xF020_C000 0xF020_FFFF

4.10.2 Main Features of Flash Module

• Support for multiple flash banks for program and/or data storage

• Simultaneous read access on a bank while performing program or erase operation on any other bank

• Integrated state machines to automate flash erase and program operations

• Pipelined mode operation to improve instruction access interface bandwidth

• Support for Single Error Correction Double Error Detection (SECDED) block inside Cortex-R4F CPU

– Error address is captured for host system debugging

• Support for a rich set of diagnostic features

Copyright © 2012, Texas Instruments Incorporated System Information and Electrical Specifications 81

Submit Documentation Feedback

Loading...

Loading...