RM46L852

SPNS185 –SEPTEMBER 2012

www.ti.com

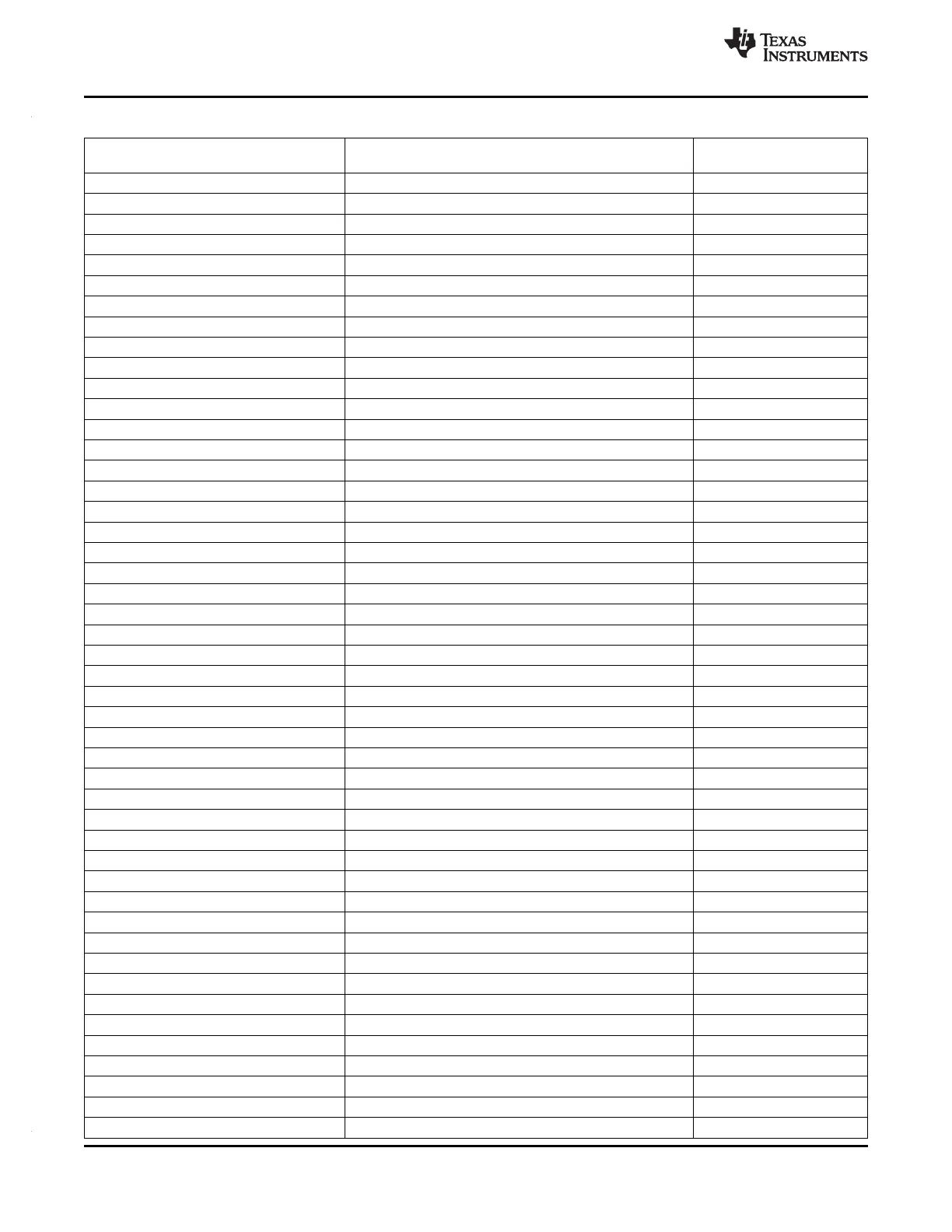

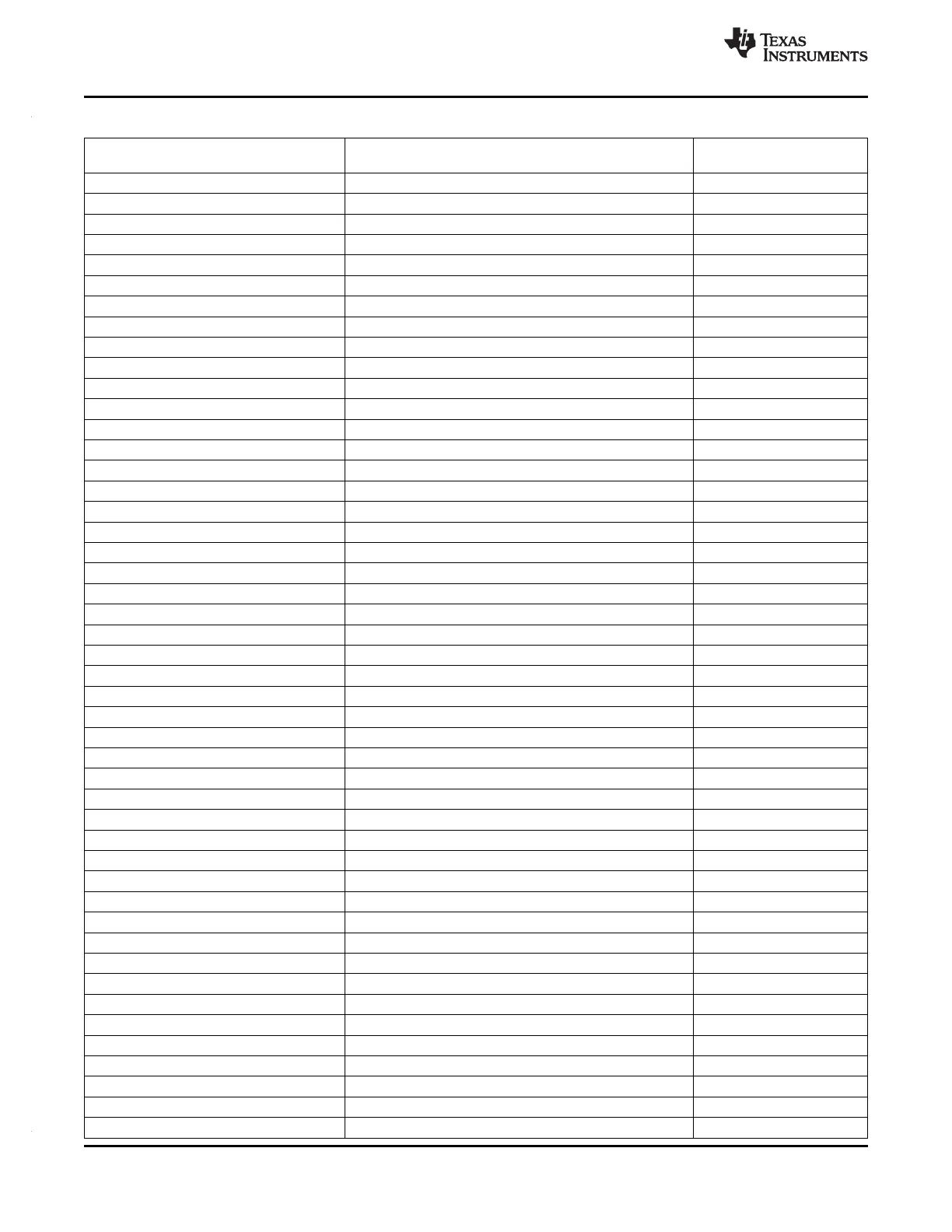

Table 4-32. Interrupt Request Assignments (continued)

Modules Interrupt Sources Default VIM Interrupt

Channel

LIN LIN level 1 interrupt 27

MIBADC1 MIBADC1 sw group 2 interrupt 28

DCAN1 DCAN1 level 1 interrupt 29

SPI2 SPI2 level 1 interrupt 30

MIBADC1 MIBADC1 magnitude compare interrupt 31

Reserved Reserved 32

DMA FTCA interrupt 33

DMA LFSA interrupt 34

DCAN2 DCAN2 level 0 interrupt 35

MIBSPI3 MIBSPI3 level 0 interrupt 37

MIBSPI3 MIBSPI3 level 1 interrupt 38

DMA HBCA interrupt 39

DMA BTCA interrupt 40

EMIF AEMIFINT3 41

DCAN2 DCAN2 level 1 interrupt 42

DCAN1 DCAN1 IF3 interrupt 44

DCAN3 DCAN3 level 0 interrupt 45

DCAN2 DCAN2 IF3 interrupt 46

Reserved Reserved 47

Reserved Reserved 48

SPI4 SPI4 level 0 interrupt 49

MIBADC2 MibADC2 event group interrupt 50

MIBADC2 MibADC2 sw group1 interrupt 51

Reserved Reserved 52

MIBSPI5 MIBSPI5 level 0 interrupt 53

SPI4 SPI4 level 1 interrupt 54

DCAN3 DCAN3 level 1 interrupt 55

MIBSPI5 MIBSPI5 level 1 interrupt 56

MIBADC2 MibADC2 sw group2 interrupt 57

Reserved Reserved 58

MIBADC2 MibADC2 magnitude compare interrupt 59

DCAN3 DCAN3 IF3 interrupt 60

FMC FSM_DONE interrupt 61

Reserved Reserved 62

N2HET2 N2HET2 level 0 interrupt 63

SCI SCI level 0 interrupt 64

HET TU2 HET TU2 level 0 interrupt 65

I2C I2C level 0 interrupt 66

USB Host OHCI_INT 67

USB Device USB_FUNC.IRQISOON 68

USB Device USB_FUNC.IRQGENION 69

USB Device USB_FUNC.IRQNONISOON 70

USB Device not (USB_FUNC.DSWAKEREQON) 71

USB Device USB_FUNC.USBRESETO 72

N2HET2 N2HET2 level 1 interrupt 73

SCI SCI level 1 interrupt 74

HET TU2 HET TU2 level 1 interrupt 75

96 System Information and Electrical Specifications Copyright © 2012, Texas Instruments Incorporated

Submit Documentation Feedback

Loading...

Loading...