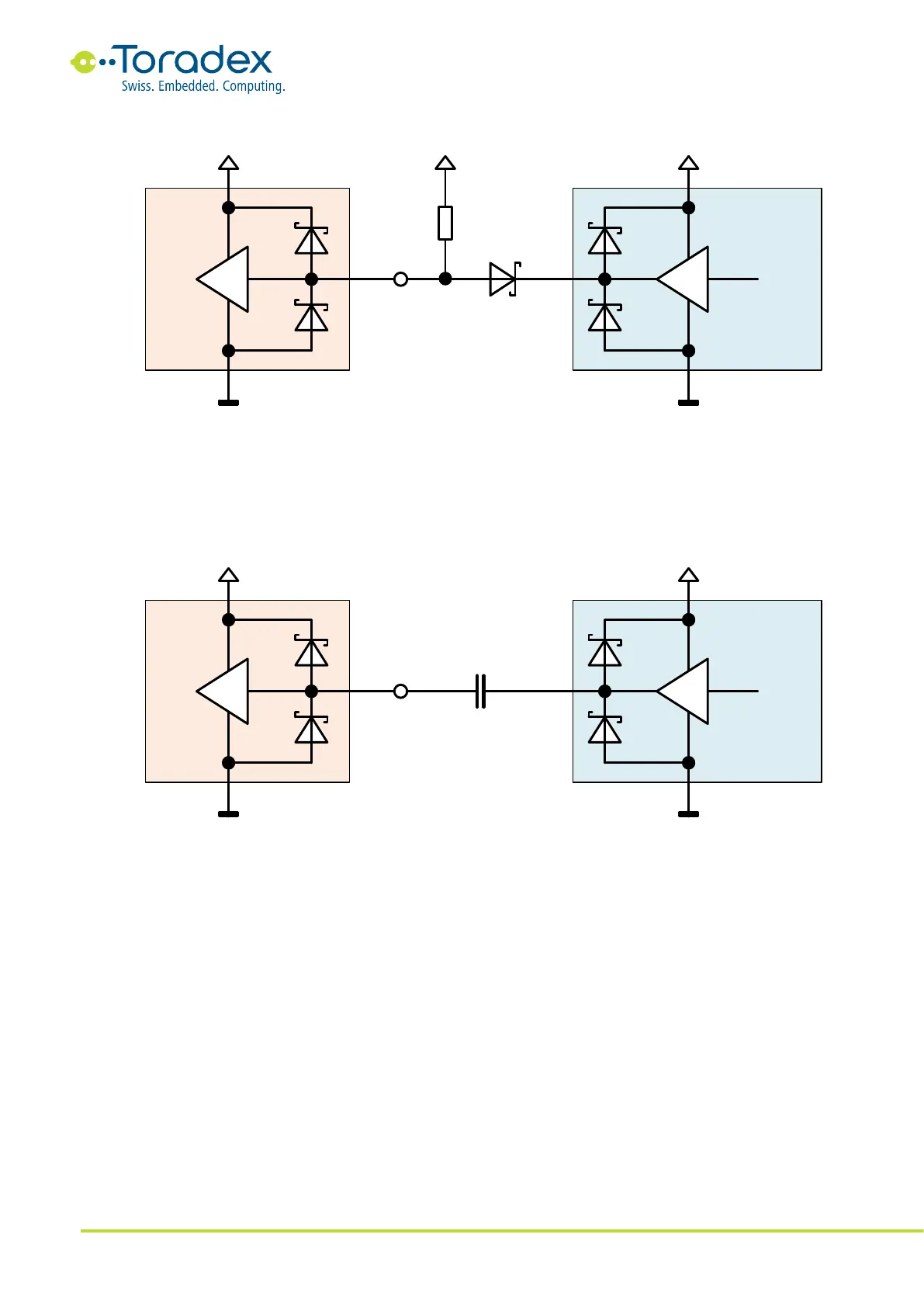

Figure 48: Diode circuit for backfeeding prevention with an external pull-up resistor

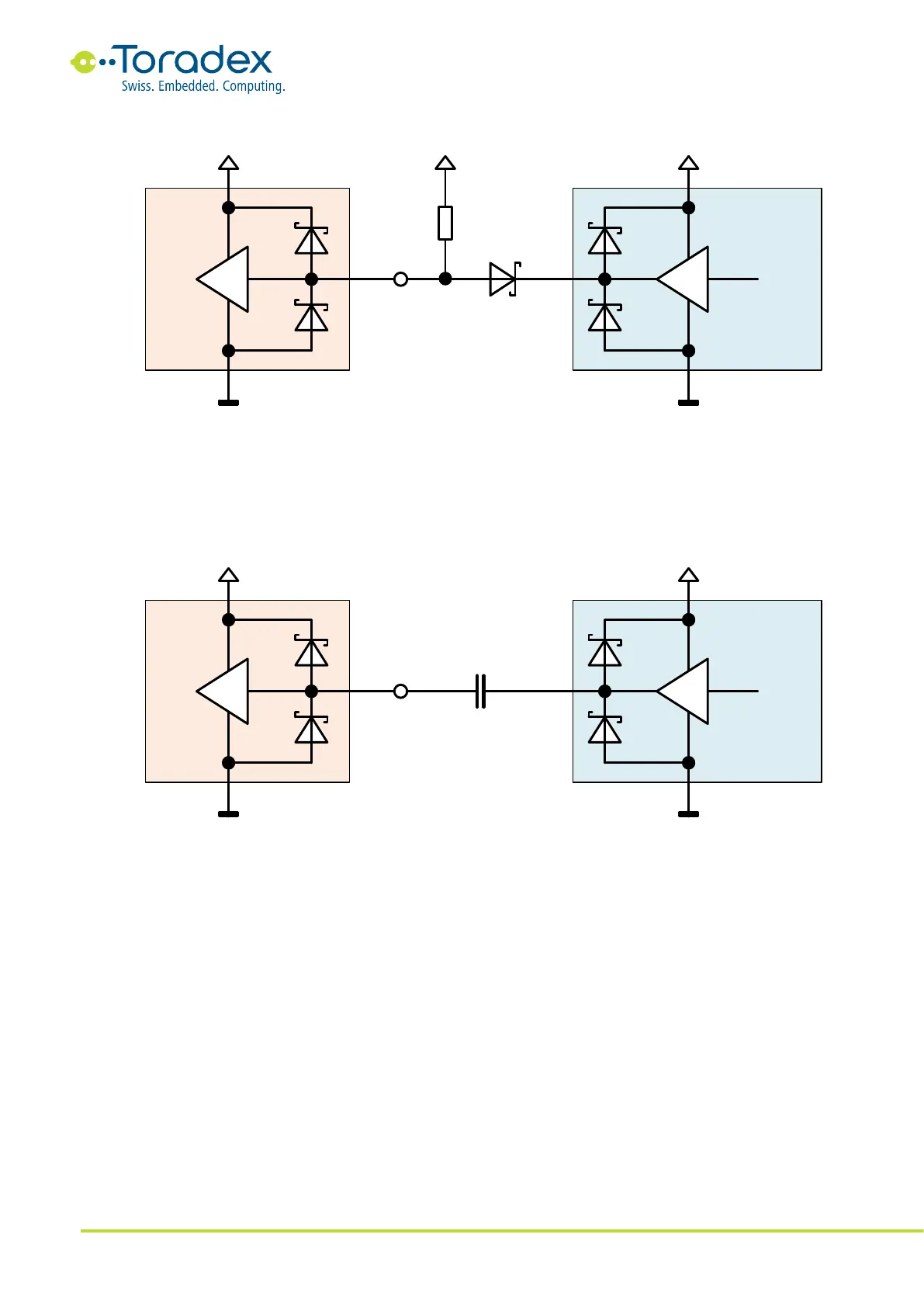

3.7.5.8 Capacitive Coupling

Some high-speed signals allow (or require) capacitive coupling. Capacitive coupling blocks all DC

current and eliminates backfeeding caused by a DC offset of high-speed signals. Most high-speed

interfaces and differential clocks (e.g., LVPECL, CML) use capacitive coupling nowadays. Typical

signals using capacitive coupling are PCIe, SATA, DisplayPort, and the SuperSpeed signals of USB.

Figure 49: Capacitive coupled signals

Loading...

Loading...