ZCU102 Evaluation Board User Guide www.xilinx.com 65

UG1182 (v1.2) March 20, 2017

Chapter 3: Board Component Descriptions

16-bit color depth at 1080p (1920 x 1080 / 60 Hz). The SN65DP159RGZ device can

automatically configure itself as a re-driver at data rates <1 Gb/s, or as a re-timer at more

than this data rate. This feature can be turned off through I2C programming.

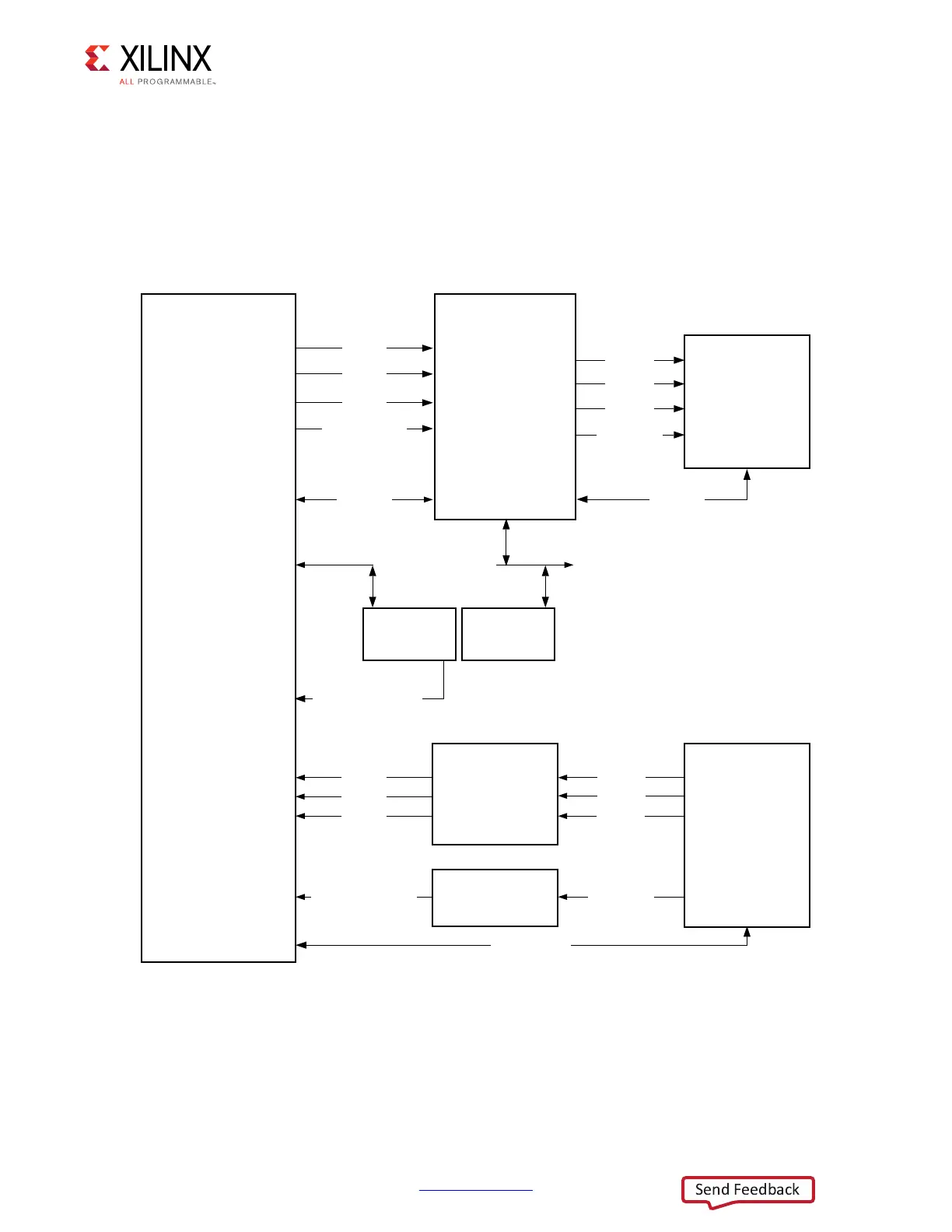

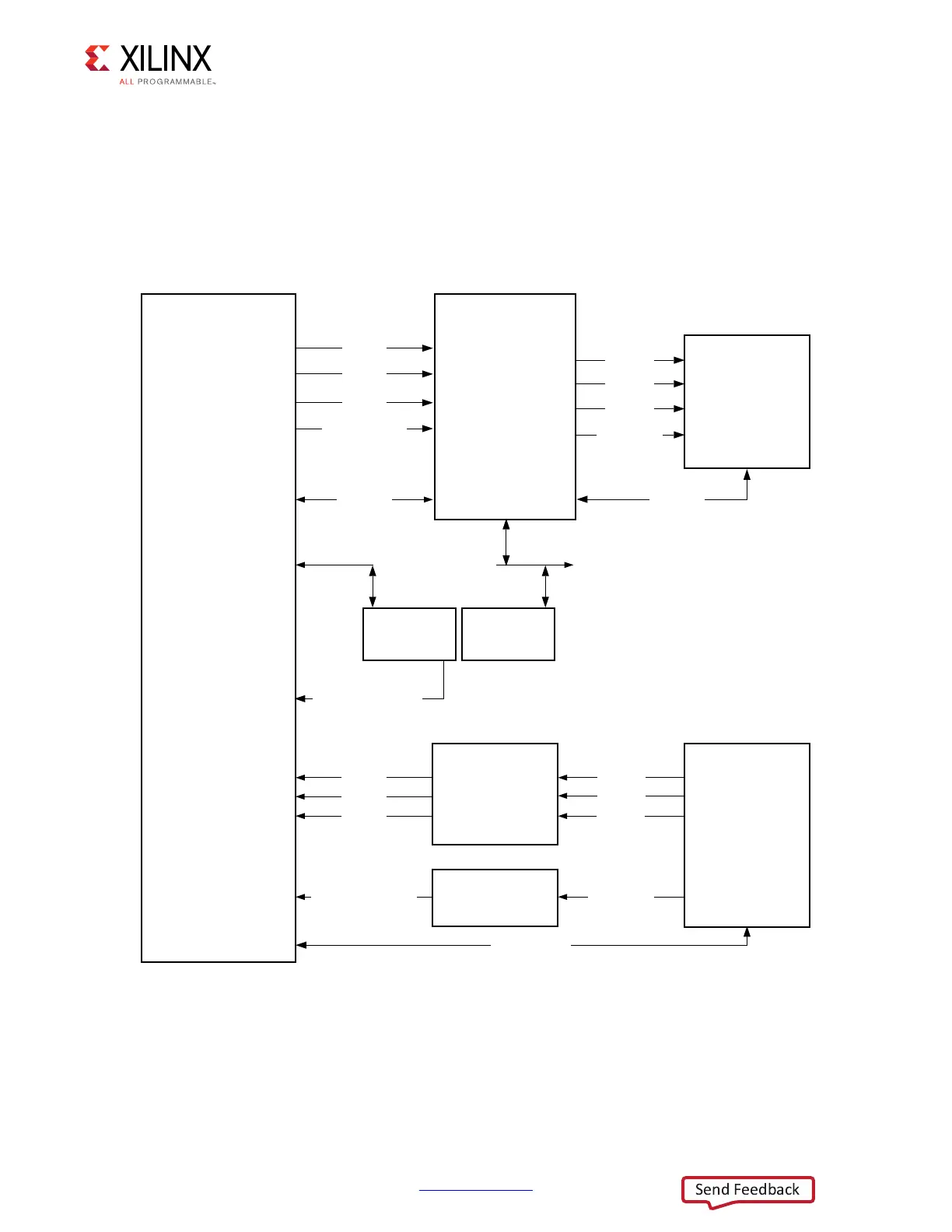

The HDMI video output block diagram is shown in Figure 3-23, the interface circuit in

Figure 3-24. The connections between the codec and the XCZU9EG MPSoC are listed in

Table 3-29.

X-Ref Target - Figure 3-23

Figure 3-23: HDMI Interface Block Diagram

3/6LGH

+'0,

,3

+'0,B

'5,9(5

61'3

+'0,B

+'0,B

7;B&/.B/9'6

&B65&

&B&7/B+'0,B287

6

(','

((3520

70'6*7+

7HUPLQDWLRQ

1HWZRUN

&/.%8))(5

+'0,B,1

+'0,B287

70'6B

70'6B

70'6B

70'6B&/.

&B61.

7;B*7+B5()B&/.

+'0,B

+'0,B

+'0,B

5;B*7+B5()&/.

70'6B

70'6B

70'6B

70'6B&/.

&B+'0,B,1

;

Loading...

Loading...