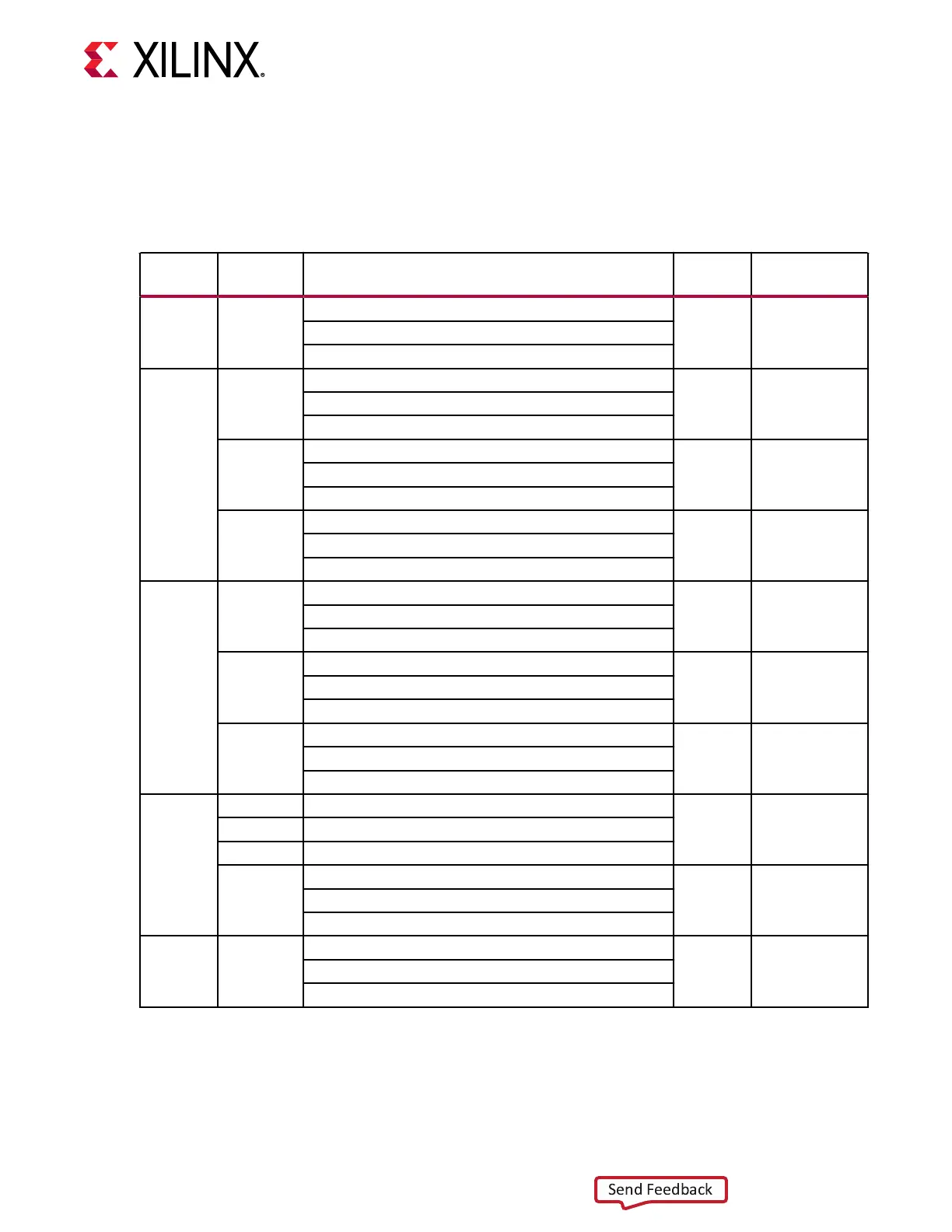

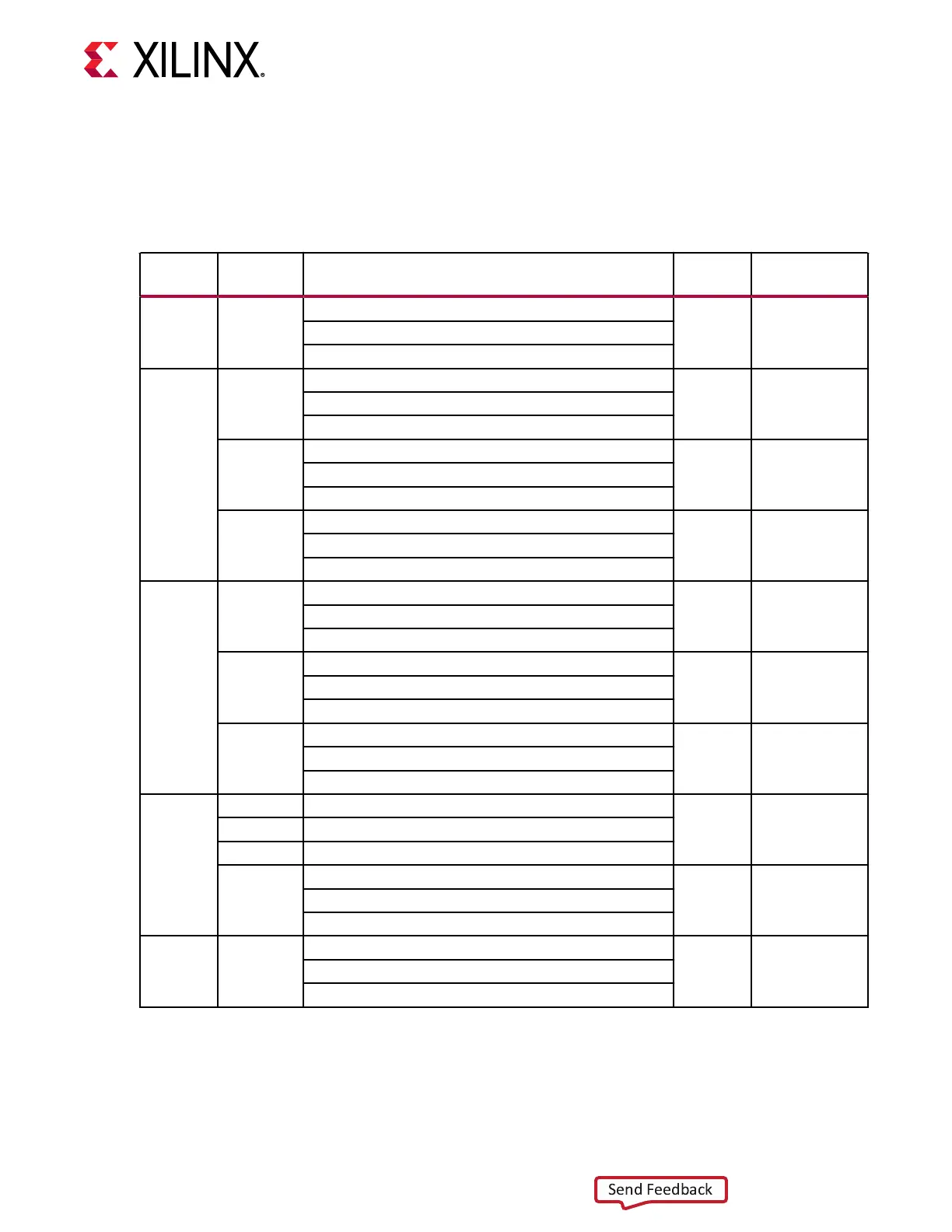

Jumpers

The following table lists the default jumper sengs.

Table 3: Default Jumper Settings

Callout

Reference

Design

Function Default

Schematic

Page

1 J1

POR_OVERRIDE

2-3 3

1-2: Enable

2-3: Disable

2

J2

SYSMON I2C Address

ON 3

OFF: SYSMON_VP_R floating

ON: SYSMON_VP_P pulled down

J3

SYSMON I2C Address

ON 3

OFF: SYSMON_VN_R floating

ON: SYSMON_VP_N pulled down

J4

SYSMON VREFP

1-2 31-2: 1.25V VREFP connected to fpga

2-3: VREFP connected to GND

3

J15

Reset Sequencer PS_POR_B

ON 12

OFF: Sequencer does not control PS_POR_B

ON: Sequencer can control PS_POR_B

J16

Reset Sequencer PS_SRST_B

ON 12OFF: Sequencer does not control PS_SRST_B

ON: Sequencer can control PS_SRST_B

J17

Reset Sequencer inhibit

OFF 12

OFF: Sequencer normal operation

ON: Sequencer inhibit (resets will stay asserted)

4

ULPI USB3320 U6 ULPIO_VBUS_SEL option jumper

OFF 22J19 ON: Selects U17 MIC2544A switch 5V for VBUS

OFF: Normal operation, VBUS from J18 USB3.0 conn.

J20

USB 3.0 Connector J18 Shield connection options

2-3 221-2: J20 shield capacitor C171 to GND

2-3: J20 shield directly to GND

5 J22

SD3.0 U107 IP4856CX25 level-trans. ref. voltage select

1-2 26

1-2: Track SD3.0 J12 socket UTIL_3V3 3.3V

2-3: GND = revert to internal voltage reference

Chapter 2: Board Setup and Configuration

UG1410 (v1.0) July 8, 2020 www.xilinx.com

ZCU208 Board User Guide 17

Loading...

Loading...