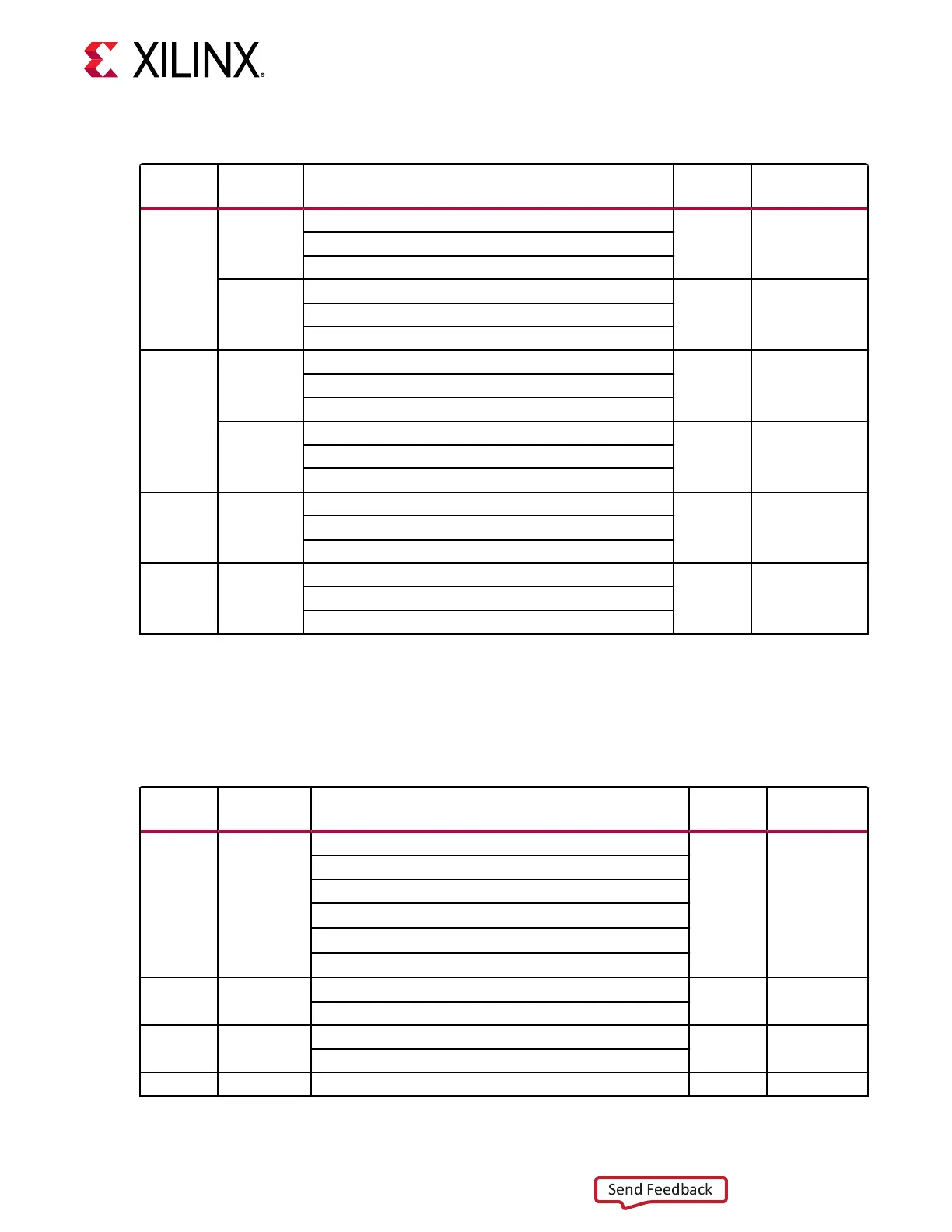

Table 3: Default Jumper Settings (cont'd)

Callout

Reference

Design

Function Default

Schematic

Page

7

J39

zSFP0 J29 LT enable jumper

OFF 38

ON: zSFP0 TX_DISABLE = GND = enabled

OFF: zSFP0 TX_DISABLE = high = disabled

J44

zSFP1 J29 LL enable jumper

OFF 38

ON: zSFP1 TX_DISABLE = GND = enabled

OFF: zSFP1 TX_DISABLE = high = disabled

8

J32

zSFP2 J29 RT enable jumper

OFF 38

ON: zSFP2 TX_DISABLE = GND = enabled

OFF: zSFP2 TX_DISABLE = high = disabled

J35

zSFP3 J29 RL enable jumper

OFF 38ON: zSFP3 TX_DISABLE = GND = enabled

OFF: zSFP3 TX_DISABLE = high = disabled

9 J10

ZU48DR RFSoC U1 ADC Bank 224 ADC_REXT select

OFF 9

ON: Bank 224 ADC_REXT pin AF9 = GND

OFF: Bank 224 ADC_REXT pin AF9 = 2.49K to GND

10 J12

ZU48DR RFSoC U1 DAC Bank 228 DAC_REXT select

OFF 10ON: Bank 228 DAC_REXT pin U9 = GND

OFF: Bank 228 DAC_REXT pin U9 = 2.49K to GND

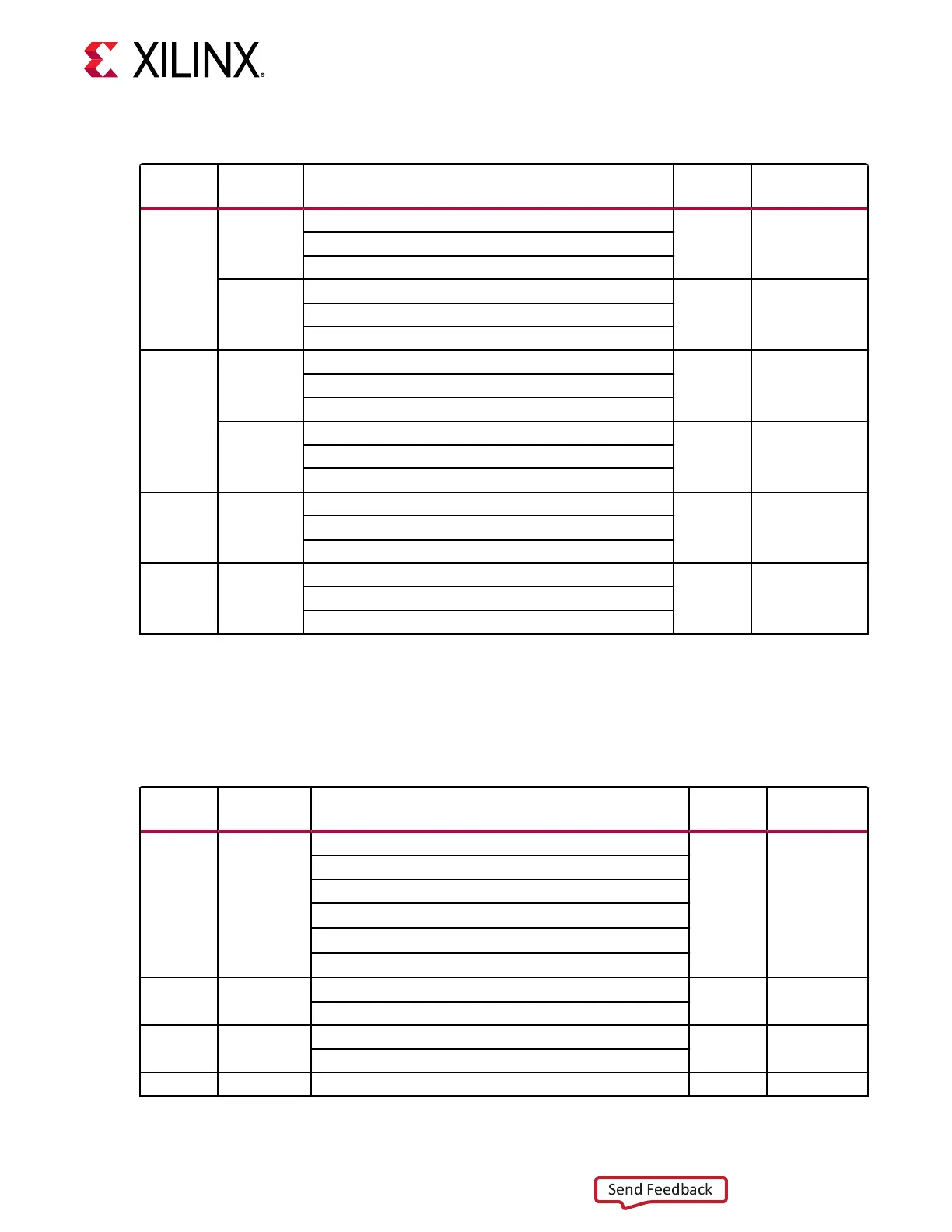

Switches

The following table lists the default switch sengs.

Table 4: Default Switch Settings

Callout

Reference

Design

Function Default

Schematic

Page

11 SW2

RFSoC U1 mode 4-pole DIP switch

0010

12

Switch OFF = 1 = High; ON = 0 = Low

Mode = SW1[4:1] = Mode[3:0]

JTAG = ON,ON,ON,ON = 0000

QSPI32 = ON,ON,OFF,ON = 0010

SD = OFF,OFF,OFF,ON = 1110

12 SW6

MSP432 U38 5-pole GPIO DIP switch

11111

30

Switch OFF = 1 = High; ON = 0 = Low

13 SW14

GPIO 8-pole DIP switch

00000000

40

Switch OFF = 0 = Low; ON = 1 = High

14 SW15 Main power slide switch OFF 46

Chapter 2: Board Setup and Configuration

UG1410 (v1.0) July 8, 2020 www.xilinx.com

ZCU208 Board User Guide 18

Loading...

Loading...