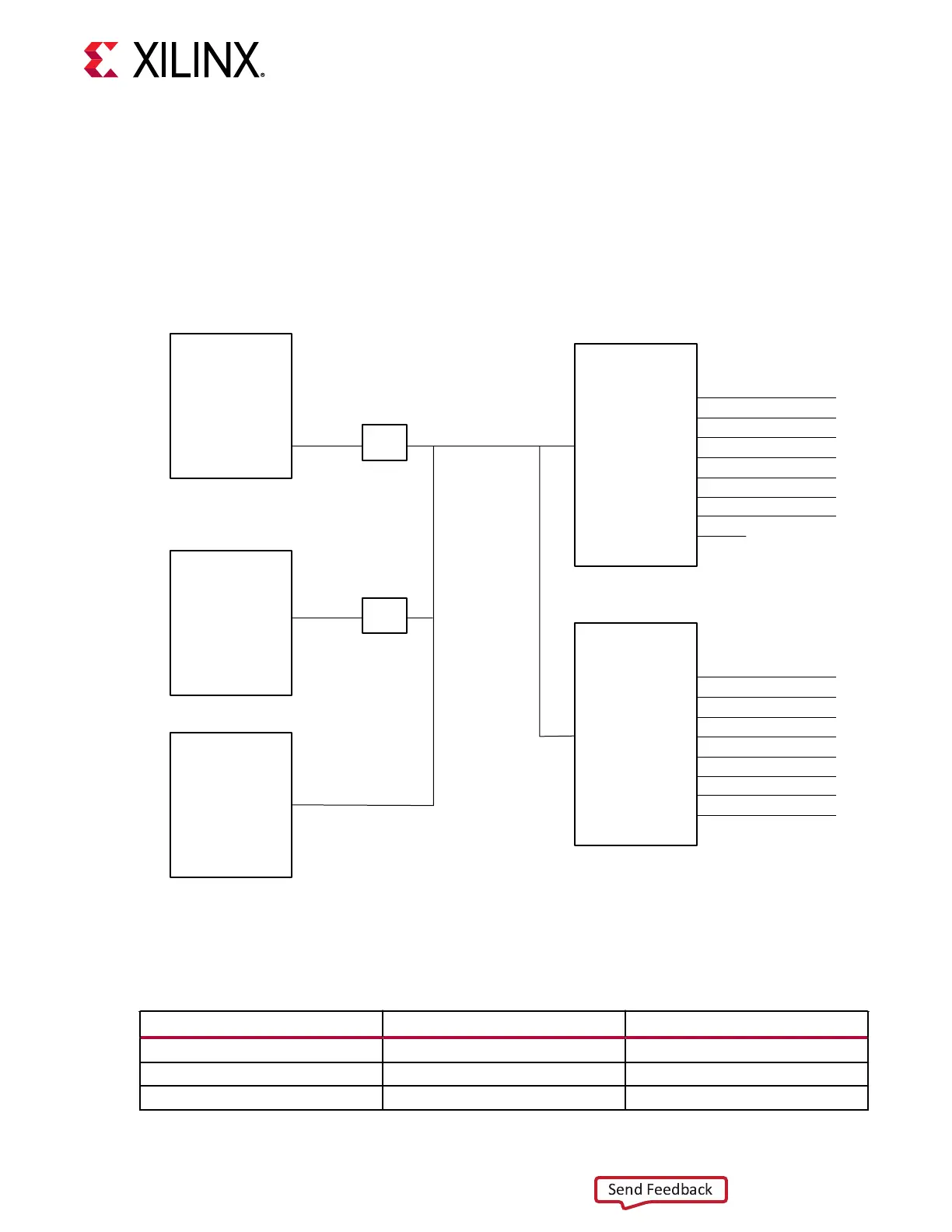

I2C bus I2C1 connects RFSoC U1 PS Bank 500, PL bank 89, and system controller U38 to two

I2C switches (TCA9548A U20 and U22). These I2C1 connecons enable I2C communicaons

with various I2C capable target devices. TCA9548A U20 is pin-strapped to respond to I2C

address 0x74. TCA9548A U22 is pin-strapped to respond to I2C address 0x75.

The following gure shows a high-level view of the I2C1 bus connecvity.

Figure 8: I2C1 Bus Topology

TCA9548A

SD0/SC0

SD1/SC1

SD2/SC2

SD3/SC3

SD4/SC5

SD5/SC5

SD6/SC6

SD7/SC7

IIC_EEPROM_SDA/SCL

S15341_SDA/SCL

USER_S1570__C0_SDA/SCL

USER_MGT_S1570_SDA/SCL

8A34001_SDA/SCL

CLK104_SDA/SCL

RFMC_I2C_SDA/SCL

Not Connected

SDA/SCL

BANK 500

PS I2C1

U1

BANK 89

U1

MPS430

U38

28 P4_1

29 P4_2

L/S

U18

0x74

U19

U20

I2C1_SDA/SCL

L/S

MIO17/

MIO16

PL I2C1

TCA9548A

SD0/SC0

SD1/SC1

SD2/SC2

SD3/SC3

SD4/SC5

SD5/SC5

SD6/SC6

SD7/SC7

FMCP_HSPC_II_SDA/SCL

USER_SI570_C1_SDA/SCL

SYSMON_SDA/SCL

PS_DDR4_SODIMM_SDA/SCL

SFP3_IIC_SDA/SCL

SFP2_IIC_SDA/SCL

SFP1_IIC_SDA/SCL

SFP0_IIC_SDA/SCL

SDA/SCL

0x75

U22

D9/C9

X23645-012120

The addresses of each target device on the I2C1 U20 and U22 PCA9548A switches are

idened in the following tables.

Table 11:

I2C1 TCA9548A U20 Target Device Addresses

TCA9548A U20 (Addr 0x74) Port I2C1 Bus Device Target Device Address

0 EEPROM U16 0X54

1 Si5341 Clock U43 0x76

2 USER Si570 C0 Clock U47 0X5D

Chapter 3: Board Component Descriptions

UG1410 (v1.0) July 8, 2020 www.xilinx.com

ZCU208 Board User Guide 33

Loading...

Loading...