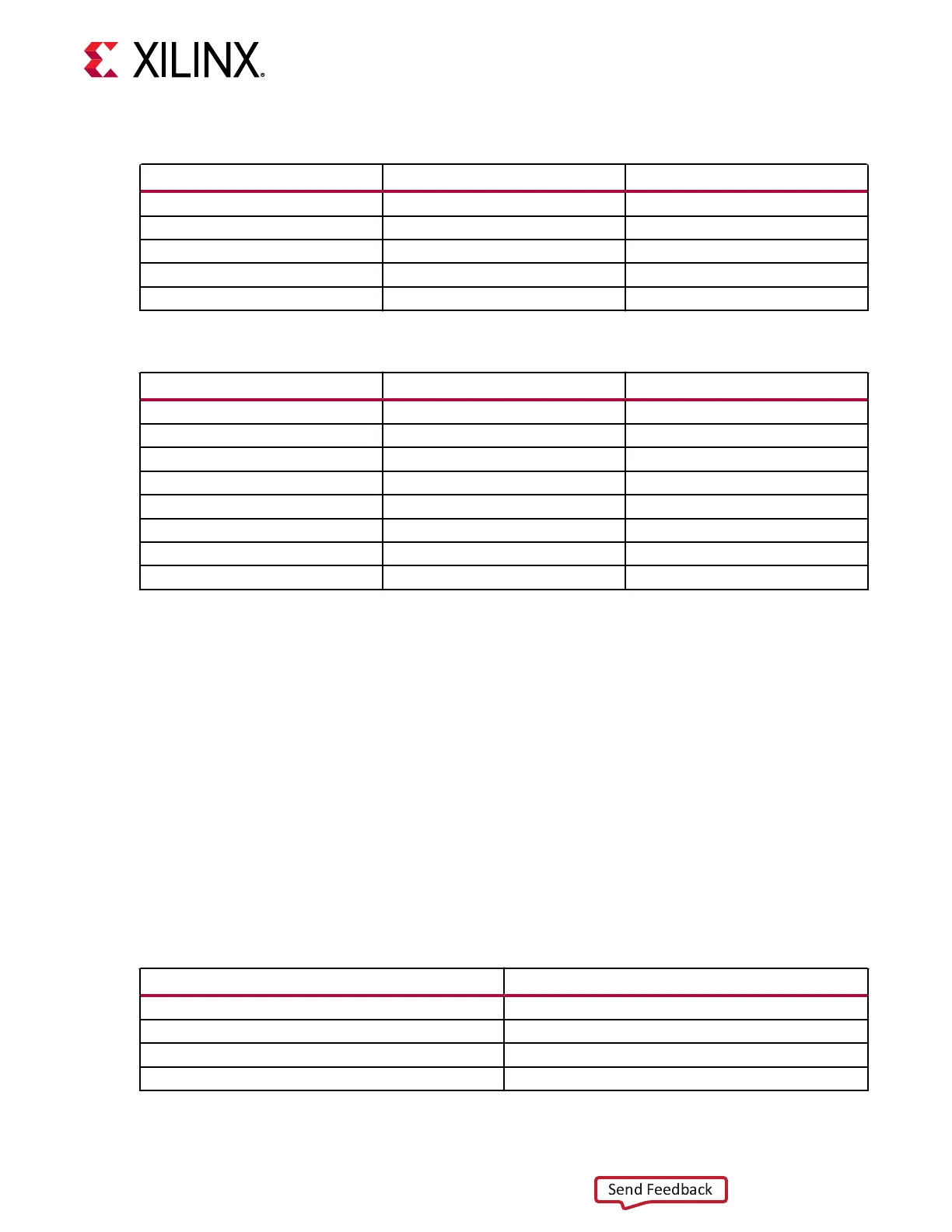

Table 11: I2C1 TCA9548A U20 Target Device Addresses (cont'd)

TCA9548A U20 (Addr 0x74) Port I2C1 Bus Device Target Device Address

3 USER MGT Si570 Clock U48 0X5D

4 8A34001 (zSFP ClK Recovery) U409 0x58

5 CLK104 Connector J101 0x2F

6 RFMC LPAF-50 Connector J82 USER

7 No Connection NA

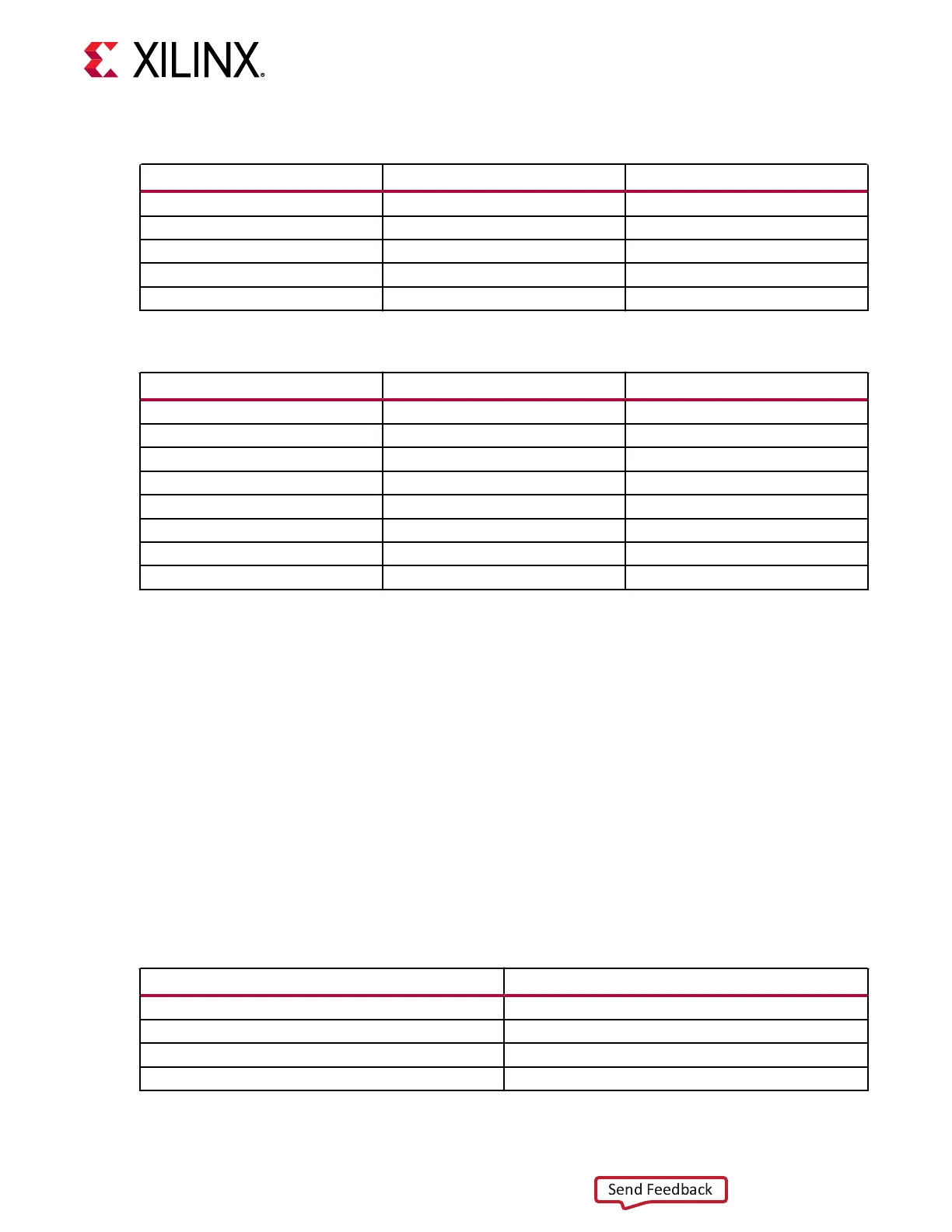

Table 12: I2C1 TCA9548A U22 Target Device Addresses

TCA9548A U22 (Addr 0x75) Port I2C1 Bus Device Target Device Address

0 FMCP HSPC J28 0x##

1 USER Si570 C1 Clock U130 0X5D

2 SYSMON U1 BANK 65 0x32

3 PS DDR4 SODIMM SKT. J48 0x51

4 SFP3 P3 0x50

5 SFP2 P2 0x50

6 SFP1 P1 0x50

7 SFP0 P0 0x50

For more informaon on the TCA9548A, TCA6416A, and PCA9544A, see the Texas Instruments

website.

The detailed Zynq UltraScale+ RFSoC connecons for the feature described in this secon are

documented in the ZCU208 board XDC le, referenced in Appendix B: Xilinx Design Constraints.

UART0 (MIO 18-19)

[Figure 2, callout 8]

This is the primary Zynq UltraScale+ RFSoC PS-side UART interface and is connected to the FTDI

U29 FT4232HL USB-to-Quad-UART Bridge port B through TXS0108E level-shier U32.

The FT4232HL U29 port assignments are listed in the following table.

Table 13: FT4232HL Port Assignments

FT4232HL U29 Zynq UltraScale+ RFSoC U1

Port A JTAG ZCU208 JTAG Chain

Port B UART0 PS_UART0 (MIO 18-19)

Port C UART2 PL_UART2 Bank 89

Port D UART3 U38 System Controller UART

Chapter 3: Board Component Descriptions

UG1410 (v1.0) July 8, 2020 www.xilinx.com

ZCU208 Board User Guide 34

Loading...

Loading...