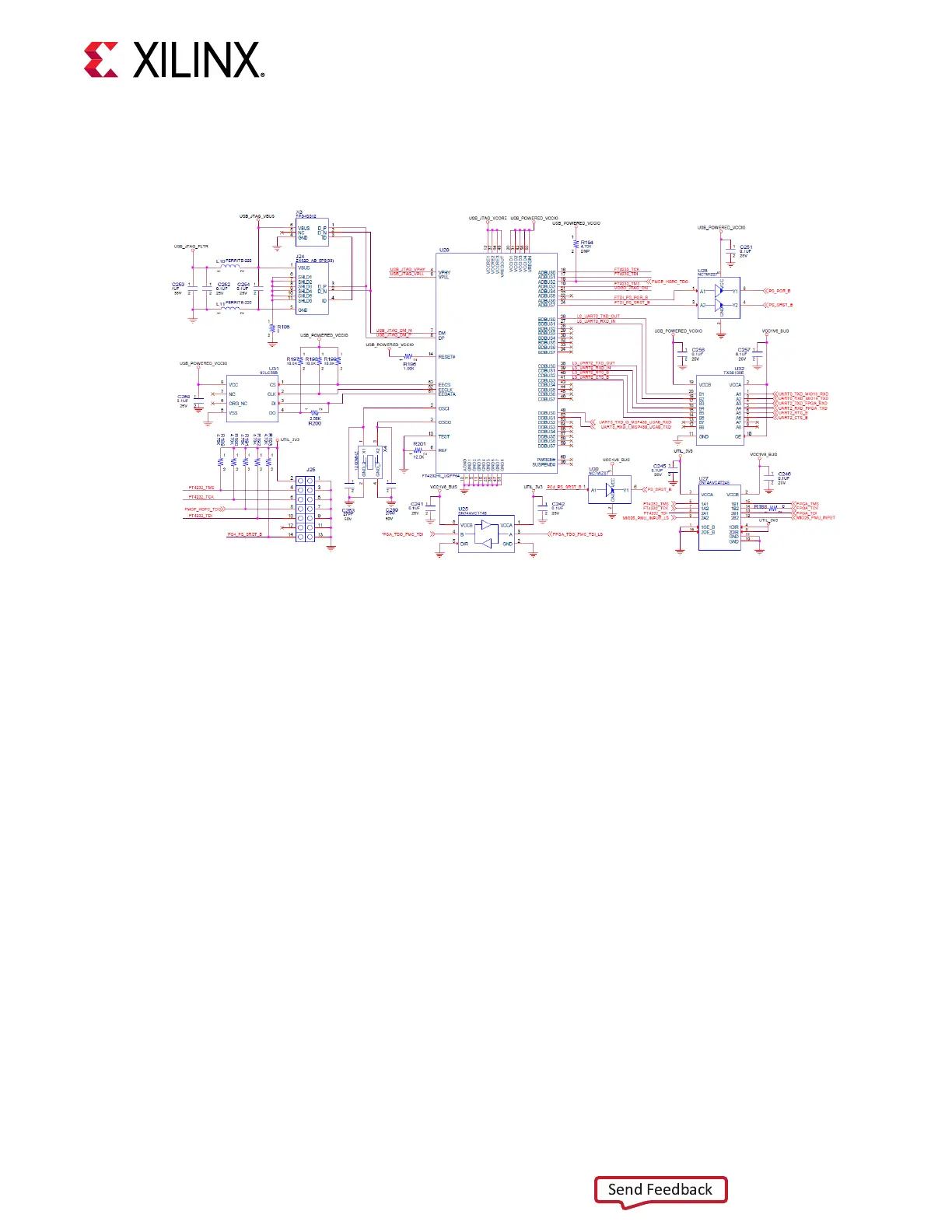

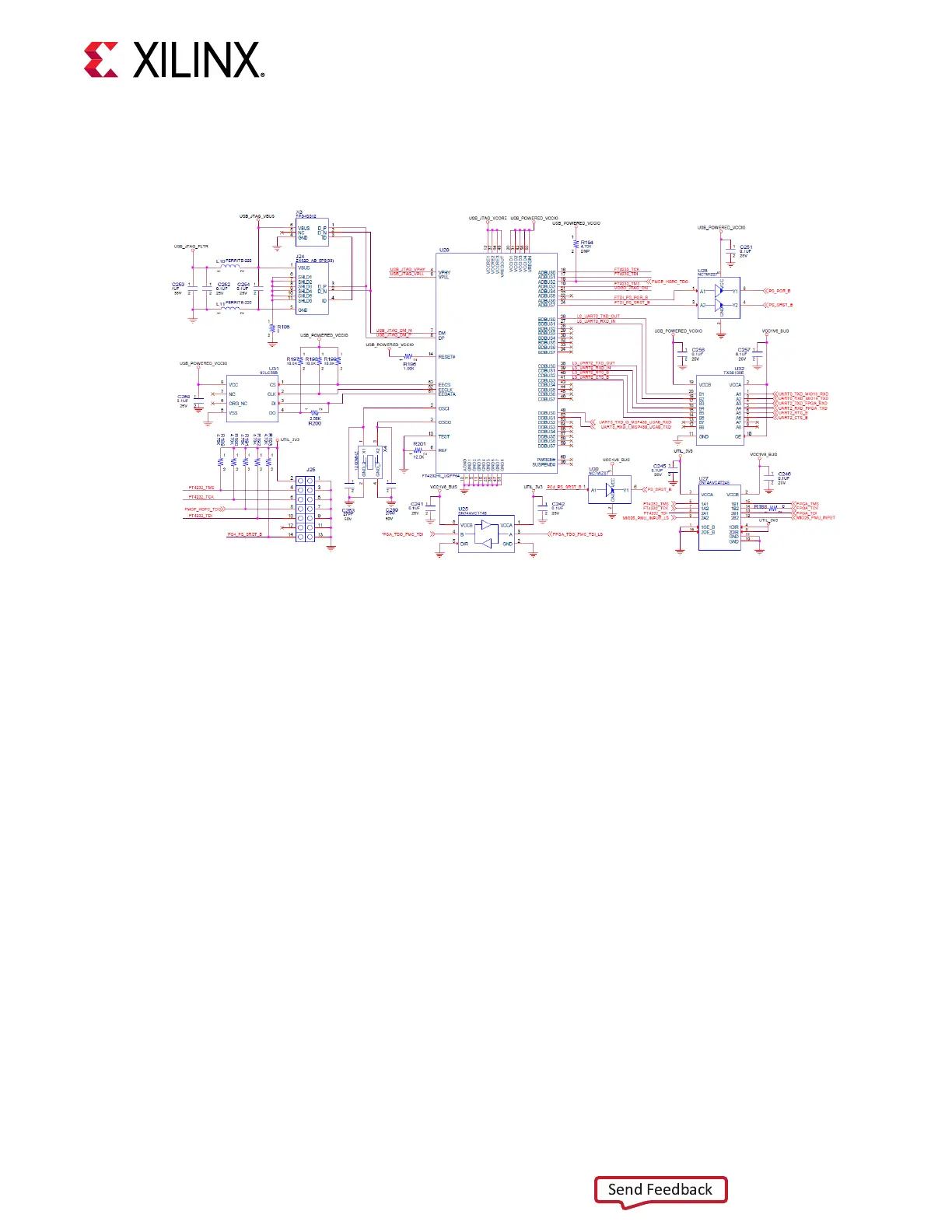

The FT4232HL interface circuit connecvity is shown in the following gure.

Figure 9: ZCU208 FT4232HL Connectivity

For more

informaon on the FT4232HL, see the Future Technology Devices Internaonal Ltd.

website.

The detailed RFSoC connecons for the feature described in this secon are documented in the

ZCU208 board XDC le, referenced in Appendix B: Xilinx Design Constraints.

GPIO (MIO 22-23)

PS-side pushbuon SW1 is connected to MIO22 (pin U1.AL27). PS-side LED DS1, physically

placed adjacent to the pushbuon, is connected to MIO23 (pin U1.AM27).

PMU GPI (MIO 26)

PS-side MIO 26 is reserved as an input to the PMU for indicang a warm boot. PS bank 501

MIO26 (U1.A34) is connected to the I2C0 U15 TCA6416A bus expander (port P02 U15.6)

through level-shier U27. See the Zynq UltraScale+ Device Technical Reference Manual (UG1085)

for details about the PMU interface.

Chapter 3: Board Component Descriptions

UG1410 (v1.0) July 8, 2020 www.xilinx.com

ZCU208 Board User Guide 35

Loading...

Loading...