ZYNQ FPGA Development Board AX7021 User Manual

l

Amazon Store: https://www.amazon.com/alinx

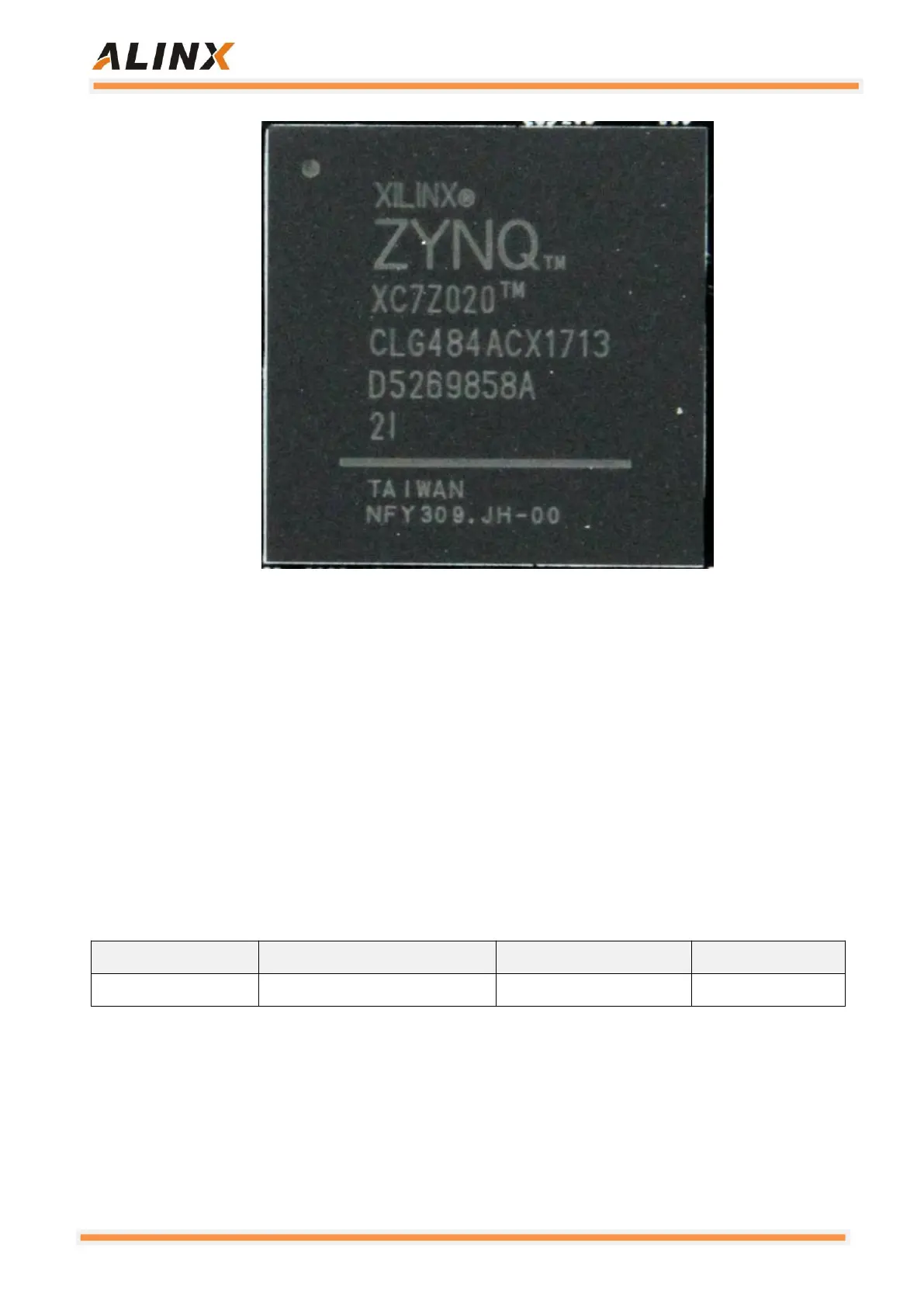

Figure 2-2-5: TheXC7Z020 chip used on the Core Board

2.3 DDR3 DRAM

The AC7021 core board is equipped with two SK Hynix DDR3 SDRAM

chips (1GB total), model H5TQ4G63AFR-PBI. The bus width of DDR3 SDRAM

is 32 bits in total. DDR3 SDRAM has a maximum operating speed of 533MHz

(data rate 1066Mbps). The DDR3 memory system is directly connected to the

memory interface of the BANK 502 of the ZYNQ Processing System (PS). The

specific configuration of DDR3 SDRAM is shown in Table 2-3-1

Table 2-3-1: DDR3 SDRAM Configuration

The hardware design of DDR3 requires strict consideration of signal

integrity. We have fully considered the matching resistor/terminal resistance,

trace impedance control, and trace length control in circuit design and PCB

design to ensure high-speed and stable operation of DDR3.

Loading...

Loading...