0.6 (2019–07–25)

Amlogic Proprietary and Confidential

Copyright © Amlogic. All rights reserved.

38

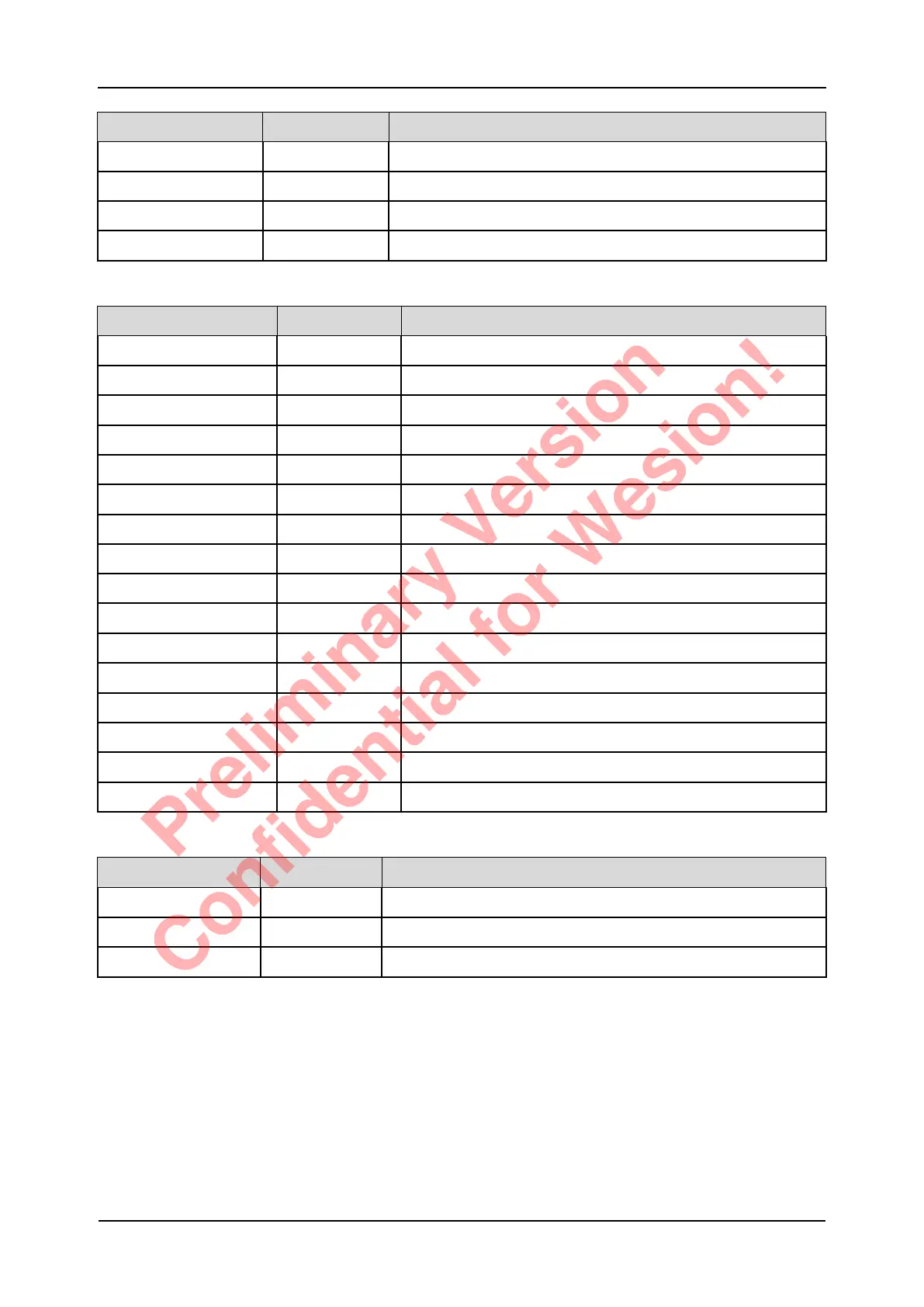

Signal Name Type Description

JTAG_B_TDO DO JTAG data output channel B

JTAG_B _TDI DI JTAG data input channel B

JTAG_B_TMS DI JTAG Test mode select input channel B

JTAG_B _CLK DI JTAG Test clock input channel B

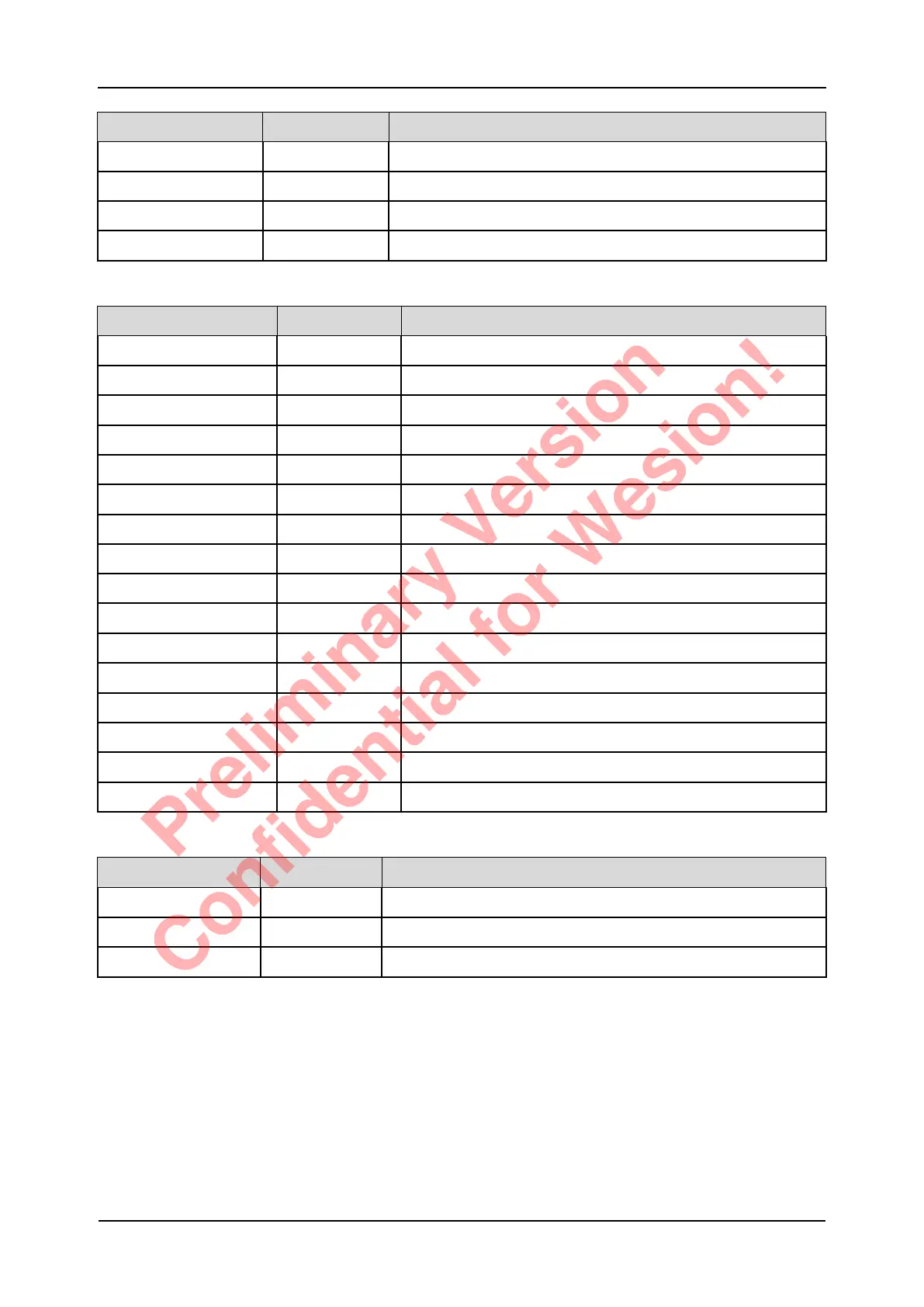

Table 4-30 Ethernet Interface Signal Description

Signal Name Type Description

ETH_LINK_LED DO Ethernet link LED indicator

ETH_ACT_LED DO Ethernet active LED indicator

ETH_RGMII_RX_CLK DI Ethernet RGMII interface receive clock input

ETH_RGMII_TX_CLK DO Ethernet RGMII transmit clock

ETH_TX_EN DO Ethernet RMII/RGMII Interface transmit enable

ETH_TXD3_RGMII DO Ethernet RGMII interface transmit data 3

ETH_TXD2_RGMII DO Ethernet RGMII interface transmit data 2

ETH_TXD1 DO Ethernet RMII/RGMII interface transmit data 1

ETH_TXD0 DO Ethernet RMII/RGMII interface transmit data 0

ETH_RX_DV DI Ethernet RMII/RGMII interface receive data valid signal

ETH_RXD3_RGMII DI Ethernet RGMII interface receive data 3

ETH_RXD2_RGMII DI Ethernet RGMII interface receive data 2

ETH_RXD1 DI Ethernet RMII/RGMII interface receive data 1

ETH_RXD0 DI Ethernet RMII/RGMII interface receive data 0

ETH_MDIO DIO Ethernet SMI interface management data input/output

ETH_MDC DO Ethernet SMI interface management clock

Table 4-31 Other Signal Description

Signal Name Type Description

WORLD_SYNC DI World clock sync input, to sync clock of multi devices

GEN_CLK_EE DO General clock output for EE domain clock, for debug

GEN_CLK_AO DO General clock output for AO domain clock, for debug

S905D3 Quick Reference Manual 4 Pinout Specification

Preliminary Version

Confidential for Wesion!

Loading...

Loading...