0.6 (2019–07–25)

Amlogic Proprietary and Confidential

Copyright © Amlogic. All rights reserved.

57

Table 5-13 RGMII Receive Timing Specification

Symbol Description Min. Typ. Max Unit Notes

tRX_CLK RGMII RX_

CLK clock

period

8 ns 125MHz from

PHY

tSETUP RXD[3:0] &

RX_DV setup

time (PHY in-

ternal delay

enabled)

1.2 ns From PHY

tHOLD RXD[3:0] &

RX_DV hold

time (PHY in-

ternal delay

enabled)

1.2 ns From PHY

tSKEW RXD[3:0] &

RX_DV skew

between

these 5 sig-

nals (PHY in-

ternal delay

disabled)

-0.5 0.5 ns From PHY

When PHY internal delay is enabled, check setup/hold timing.

When PHY internal delay is disabled, check signal skew.

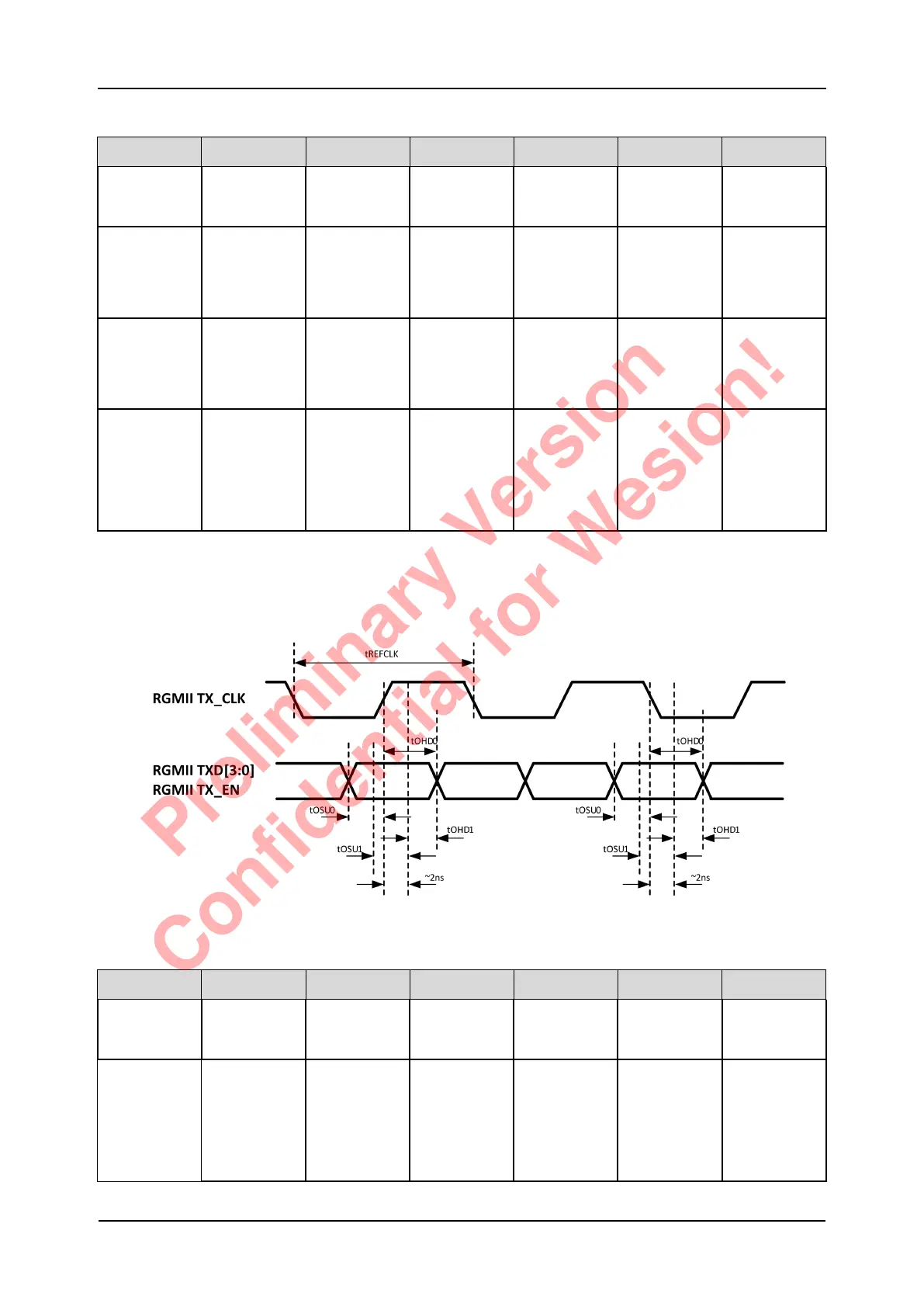

Figure 5-17 RGMII Transmit Timing Diagram

Table 5-14 RGMII Transmit Timing Specification

Symbol Description Min. Typ. Max Unit Notes

tTX_CLK RGMII TX_

CLK clock

period

8 ns 125MHz to

PHY

tOSU TXD & TX_

EN setup time

to rising edge

of RGMII

clock (no

clock delay

added)

1 ns From PHY

S905D3 Quick Reference Manual 5 Operating Conditions

Preliminary Version

Confidential for Wesion!

Loading...

Loading...