147

7679H–CAN–08/08

AT90CAN32/64/128

14.2.1 Definitions

The following definitions are used extensively throughout the section:

14.3 Timer/Counter Clock Sources

The Timer/Counter can be clocked by an internal synchronous or an external asynchronous

clock source. The clock source is selected by the clock select logic which is controlled by the

clock select (CS22:0) bits located in the Timer/Counter control register (TCCR2).The clock

source clk

T2

is by default equal to the MCU clock, clk

I/O

. When the AS2 bit in the ASSR Register

is written to logic one, the clock source is taken from the Timer/Counter Oscillator connected to

TOSC1 and TOSC2 or directly from TOSC1. For details on asynchronous operation, see “Asyn-

chronous Status Register – ASSR” on page 160. For details on clock sources and prescaler, see

“Timer/Counter2 Prescaler” on page 163.

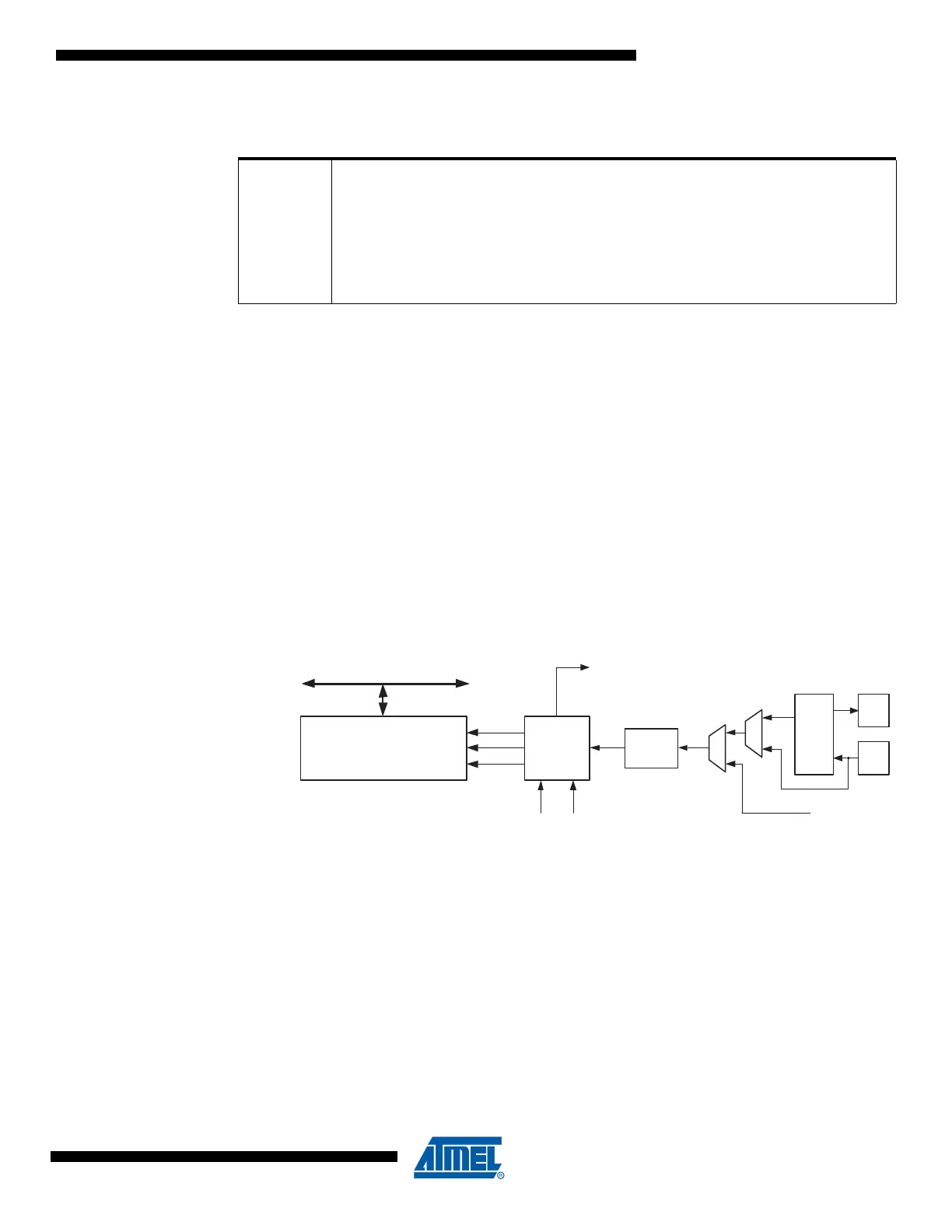

14.4 Counter Unit

The main part of the 8-bit Timer/Counter is the programmable bi-directional counter unit. Figure

14-2 shows a block diagram of the counter and its surrounding environment.

Figure 14-2. Counter Unit Block Diagram

Figure 14-3.

Signal description (internal signals):

count Increment or decrement TCNT2 by 1.

direction Selects between increment and decrement.

clear Clear TCNT2 (set all bits to zero).

clk

T2

Timer/Counter clock.

top Signalizes that TCNT2 has reached maximum value.

bottom Signalizes that TCNT2 has reached minimum value (zero).

BOTTOM The counter reaches the BOTTOM when it becomes zero (0x00).

MAX The counter reaches its MAXimum when it becomes 0xFF (decimal 255).

TOP The counter reaches the TOP when it becomes equal to the highest value in the

count sequence. The TOP value can be assigned to be the fixed value 0xFF

(MAX) or the value stored in the OCR2A Register. The assignment is depen-

dent on the mode of operation.

DATA BUS

TCNTn Control Logic

count

TOVn

(Int.Req.)

topbottom

direction

clear

TOSC2

T/C

Oscillator

TOSC1

Prescaler

clk

I/O

clk

Tn

clk

TnS

Loading...

Loading...