75

7679H–CAN–08/08

AT90CAN32/64/128

Table 9-4 and Table 9-5 relates the alternate functions of Port A to the overriding signals shown

in Figure 9-5 on page 72.

Note: 1. ADA is short for ADdress Active and represents the time when address is output. See “Exter-

nal Memory Interface” on page 27 for details.

Note: 1. ADA is short for ADdress Active and represents the time when address is output. See “Exter-

nal Memory Interface” on page 27 for details.

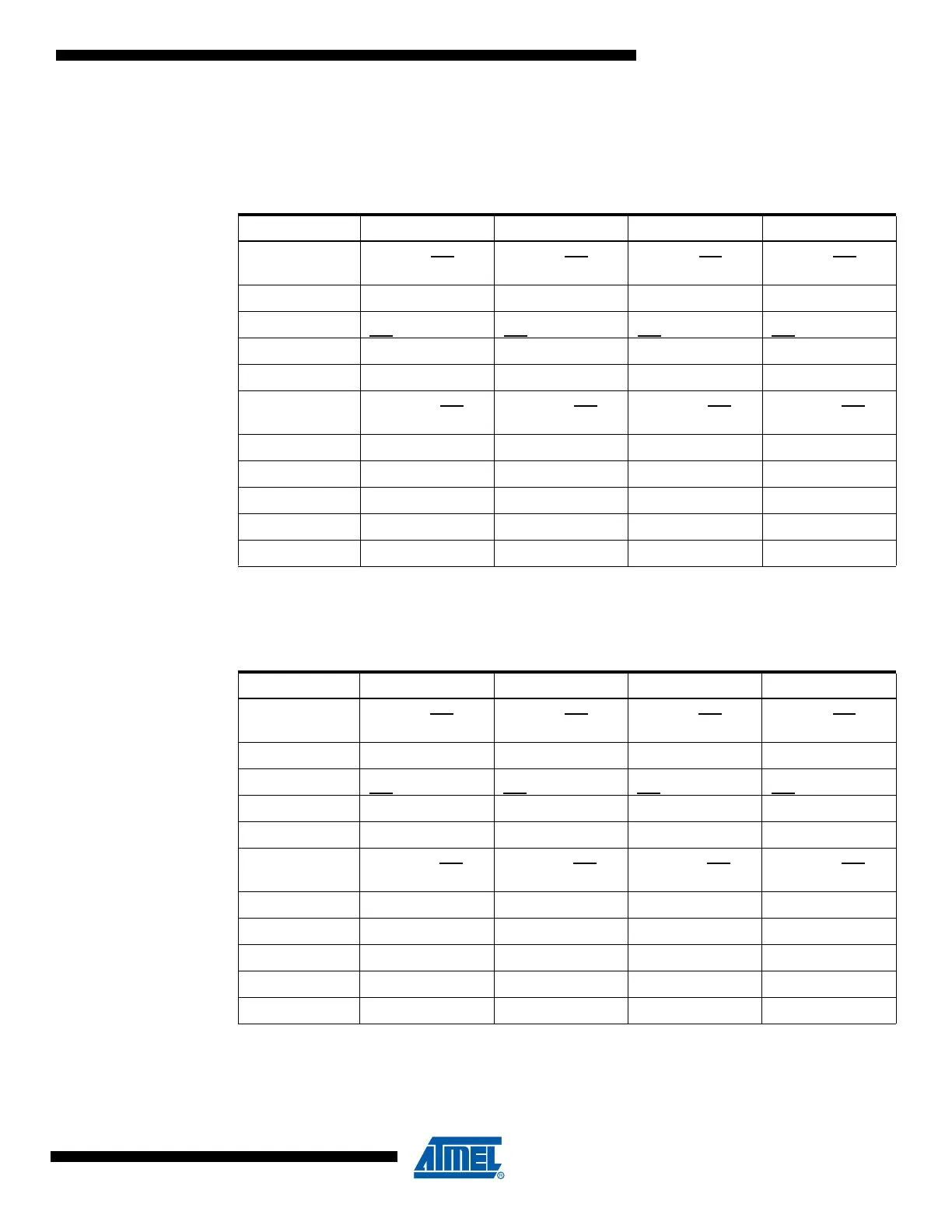

Table 9-4. Overriding Signals for Alternate Functions in PA7..PA4

Signal Name PA7/AD7 PA6/AD6 PA5/AD5 PA4/AD4

PUOE

SRE •

(ADA

(1)

+ WR)

SRE •

(ADA

(1)

+ WR)

SRE •

(ADA

(1)

+ WR)

SRE •

(ADA

(1)

+ WR)

PUOV0000

DDOE SRE SRE SRE SRE

DDOV WR

+ ADA WR + ADA WR + ADA WR + ADA

PVOE SRE SRE SRE SRE

PVOV

A7 • ADA

(1)

+ D7

OUTPUT • WR

A6 • ADA

(1)

+ D6

OUTPUT • WR

A5 • ADA

(1)

+ D5

OUTPUT • WR

A4 • ADA

(1)

+ D4

OUTPUT • WR

PTOE0000

DIEOE0000

DIEOV0000

DI D7 INPUT D6 INPUT D5 INPUT D4 INPUT

AIO––––

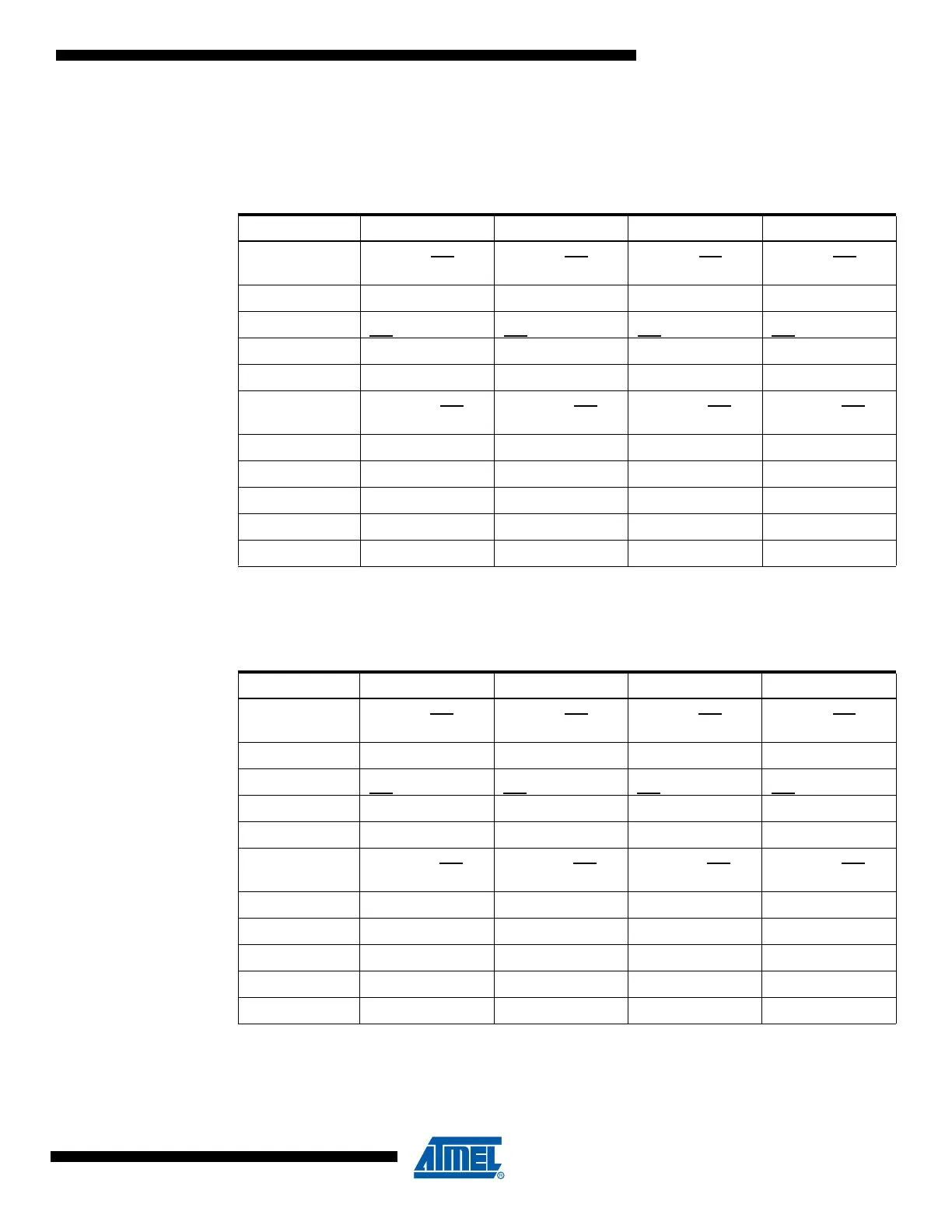

Table 9-5. Overriding Signals for Alternate Functions in PA3..PA0

Signal Name PA3/AD3 PA2/AD2 PA1/AD1 PA0/AD0

PUOE

SRE •

(ADA

(1)

+ WR)

SRE •

(ADA

(1)

+ WR)

SRE •

(ADA

(1)

+ WR)

SRE •

(ADA

(1)

+ WR)

PUOV0000

DDOE SRE SRE SRE SRE

DDOV WR

+ ADA WR + ADA WR + ADA WR + ADA

PVOE SRE SRE SRE SRE

PVOV

A3 • ADA

(1)

+ D3

OUTPUT • WR

A2 • ADA

(1)

+ D2

OUTPUT • WR

A1 • ADA

(1)

+ D1

OUTPUT • WR

A0 • ADA

(1)

+ D0

OUTPUT • WR

PTOE0000

DIEOE0000

DIEOV0000

DI D3 INPUT D2 INPUT D1 INPUT D0 INPUT

AIO––––

Loading...

Loading...