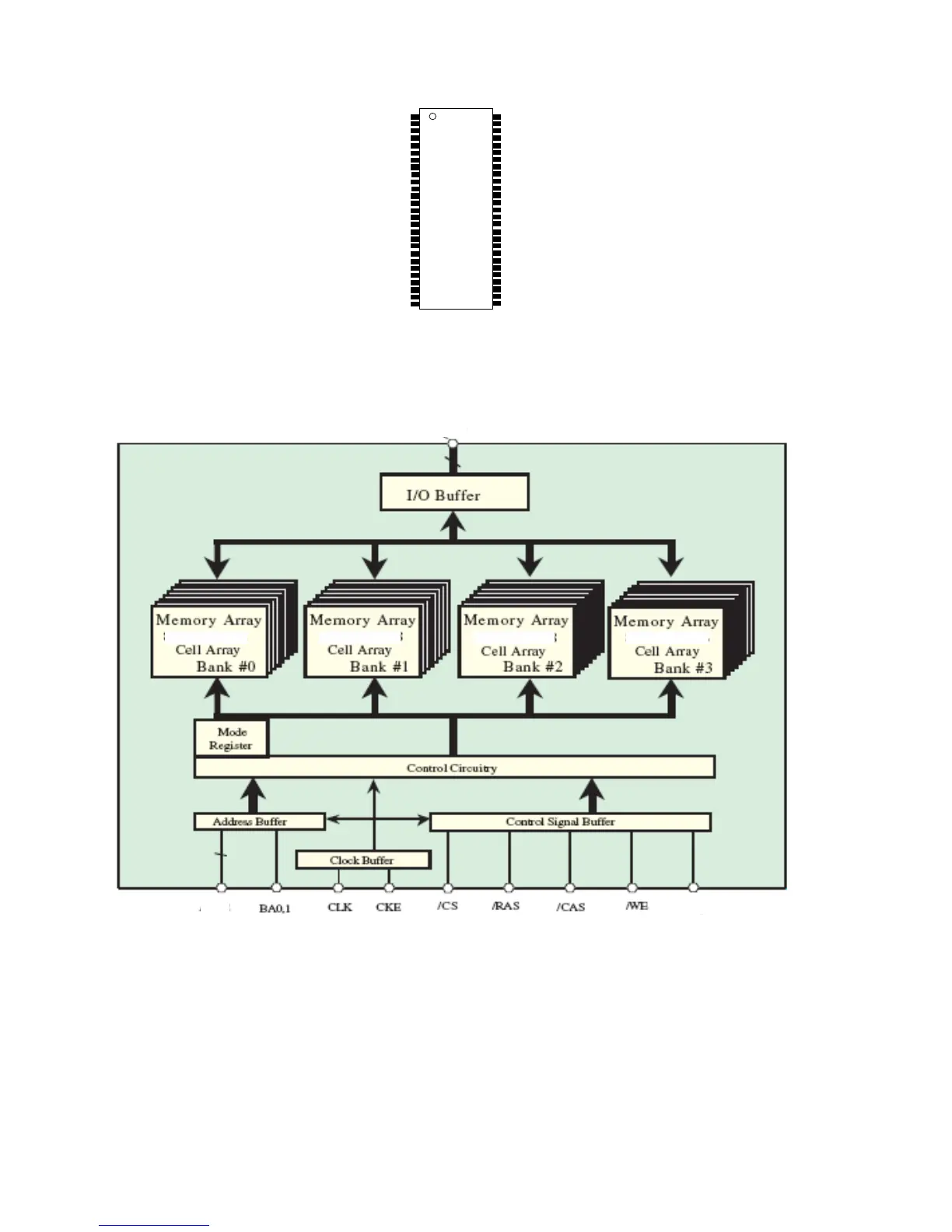

CKE : Clock Enable A0-11 : Address Input

/CS : Chip Select BA0,1 : Bank Address

/RAS : Row Address Strobe Vdd : Power Supply

/CAS : Column Address Strobe VddQ : Power Supply for Output

/WE : Write Enable Vss : Ground

DQ0-15 : Data I/O VssQ : Ground for Output

Loading...

Loading...